# **ECOSYSTEM FOR TRUSTWORTHY IT LOS 4: FORMAL SECURITY GUARANTEES FOR TRUSTWORTHY HARDWARE SUPPLY CHAINS**

Dominik Sisejkovic,

Lennart M. Reimann,

Maja Malenko,

Rainer Leupers

January 2023

Herausgeberin:

Agentur für Innovation in der Cybersicherheit GmbH

## **Disclaimer**

Die hier geäußerten Ansichten und Meinungen sind ausschließlich diejenigen der Autorinnen und Autoren und entsprechen nicht notwendigerweise denjenigen der Agentur für Innovation in der Cybersicherheit GmbH oder der Bundesregierung.

Diese Studie wurde durch die Agentur für Innovation in der Cybersicherheit GmbH beauftragt und finanziert. Eine Einflussnahme der Agentur für Innovation in der Cybersicherheit GmbH auf die Ergebnisse fand nicht statt.

## **Impressum**

Herausgeberin: Agentur für Innovation in der Cybersicherheit GmbH

Große Steinstraße 19, 06108 Halle (Saale), Germany

E-Mail: [kontakt@cyberagentur.de](mailto:kontakt@cyberagentur.de)

Internet: [www.cyberagentur.de](http://www.cyberagentur.de)

Twitter: <https://twitter.com/CybAgBund>

Die Nutzungsrechte liegen bei der Herausgeberin.

Lizenz: CC BY-NC-ND 4.0: <https://creativecommons.org/licenses/by-nc-nd/4.0/>

Erscheinungsdatum: 12.07.2023

Redaktion: Abteilung Sichere Systeme, Referat Sichere Hardware und Lieferketten

# **Los 4: Formal Security Guarantees for Trustworthy Hardware Supply Chains**

Dominik Sisejkovic, Lennart M. Reimann, Maja Malenko, Rainer Leupers

January 2023

# Contents

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| <b>I. WP1: Attacks Enabled by Malicious HW Manipulations</b>                  | <b>7</b>  |

| <b>1. Classification of Critical Assets</b>                                   | <b>9</b>  |

| 1.1. IP Owner . . . . .                                                       | 9         |

| 1.2. External Design House . . . . .                                          | 10        |

| 1.3. Foundry . . . . .                                                        | 12        |

| 1.4. Assembly . . . . .                                                       | 12        |

| 1.5. OEM . . . . .                                                            | 13        |

| 1.6. End Users . . . . .                                                      | 14        |

| <b>2. Electronics Supply Chain Threats: Hardware Manipulations</b>            | <b>16</b> |

| 2.1. Hardware Trojans . . . . .                                               | 16        |

| 2.1.1. Trojan Components . . . . .                                            | 16        |

| 2.1.2. Classifications . . . . .                                              | 17        |

| 2.1.2.1. Physical, Activation, and Action Characteristics . . . . .           | 17        |

| 2.1.2.2. Activation Mechanism and Effect . . . . .                            | 18        |

| 2.1.2.3. A Comprehensive Classification . . . . .                             | 19        |

| 2.1.2.4. Reverse-Engineering-Based Classification . . . . .                   | 20        |

| 2.1.3. Example Trojan Implementations . . . . .                               | 21        |

| 2.2. Attack Models . . . . .                                                  | 22        |

| 2.2.1. Threat Levels . . . . .                                                | 22        |

| 2.2.2. Hardware Trojans: Insertion Effort and Impact . . . . .                | 24        |

| 2.2.3. IP Owner . . . . .                                                     | 25        |

| 2.2.4. External Design House . . . . .                                        | 25        |

| 2.2.5. Foundry . . . . .                                                      | 25        |

| 2.2.6. Assembly . . . . .                                                     | 27        |

| 2.2.7. OEM . . . . .                                                          | 27        |

| 2.2.8. End Users . . . . .                                                    | 27        |

| 2.2.9. The Cooperative Scenario . . . . .                                     | 28        |

| 2.3. Threat Evaluation . . . . .                                              | 28        |

| 2.4. Open Challenges . . . . .                                                | 29        |

| <b>3. The Untrusted Design House and Foundry</b>                              | <b>30</b> |

| 3.1. The Attack Model: Assumptions . . . . .                                  | 30        |

| 3.2. Reverse Engineering . . . . .                                            | 31        |

| 3.2.1. Flow . . . . .                                                         | 31        |

| 3.2.1.1. Printed Circuit Board (PCB)-level Reverse Engineering (RE) . . . . . | 33        |

| 3.2.1.2. Chip-level RE . . . . .                                              | 34        |

| 3.2.1.3. Layout RE . . . . .                                                  | 35        |

| 3.2.1.4. Netlist RE . . . . .                                                 | 35        |

| 3.3. Open Challenges . . . . .                                                | 37        |

---

## II. WP2: State of the Art in Protection Mechanisms and Detection Methods 38

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

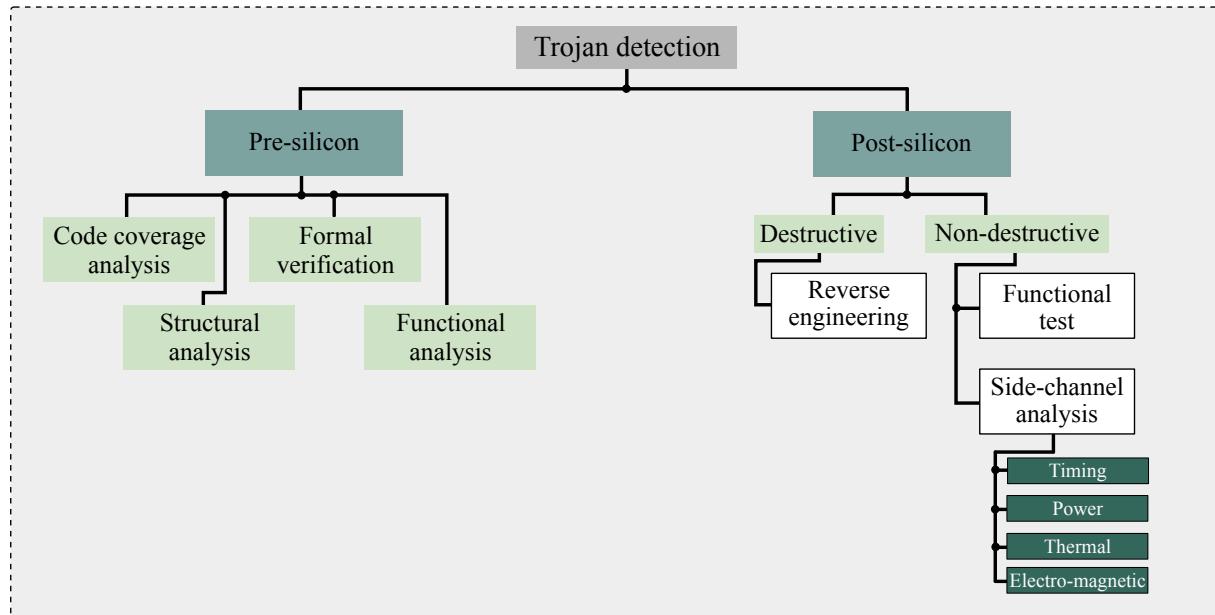

| <b>4. Detection of Malicious HW Manipulations</b>                          | <b>40</b> |

| 4.1. Pre-silicon Trojan Detection . . . . .                                | 40        |

| 4.1.1. Code Coverage Analysis . . . . .                                    | 40        |

| 4.1.2. Formal Verification . . . . .                                       | 41        |

| 4.1.2.1. Reusing Existing Verification Techniques for Security . . . . .   | 41        |

| 4.1.2.2. Equivalence Checking . . . . .                                    | 41        |

| 4.1.2.3. Security Properties Enforcement . . . . .                         | 42        |

| 4.1.3. Structural Analysis . . . . .                                       | 44        |

| 4.1.4. Functional Analysis . . . . .                                       | 45        |

| 4.2. Post-silicon Trojan Detection . . . . .                               | 45        |

| 4.2.1. Reverse Engineering (Destructive) . . . . .                         | 45        |

| 4.2.2. Functional and Fault-Model Derived Tests . . . . .                  | 46        |

| 4.2.2.1. Fault-Model Derived Tests . . . . .                               | 46        |

| 4.2.2.2. Functional Tests . . . . .                                        | 46        |

| 4.2.3. Side-Channel Signal Analysis . . . . .                              | 47        |

| 4.3. Open Challenges . . . . .                                             | 47        |

| <b>5. Protection Against Malicious HW Manipulations</b>                    | <b>48</b> |

| 5.1. Logic Locking . . . . .                                               | 48        |

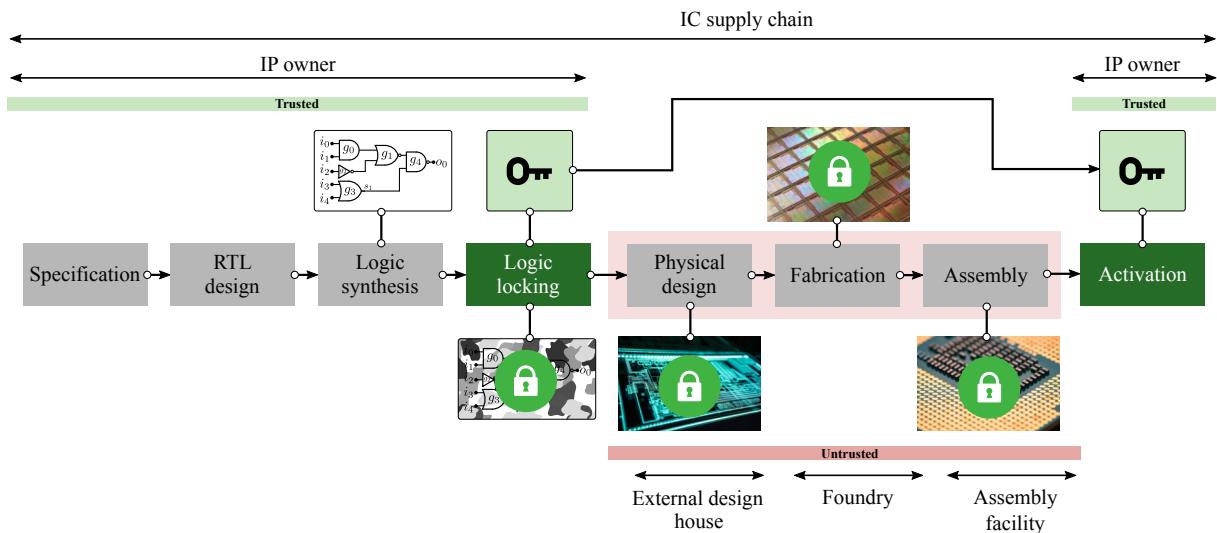

| 5.1.1. Logic Locking in the Electronics Supply Chain . . . . .             | 48        |

| 5.1.2. Attack Model . . . . .                                              | 49        |

| 5.1.3. Logic Locking vs. Reverse Engineering . . . . .                     | 50        |

| 5.1.3.1. The Metric Problem . . . . .                                      | 50        |

| 5.1.3.2. The Interplay of Attack Models . . . . .                          | 50        |

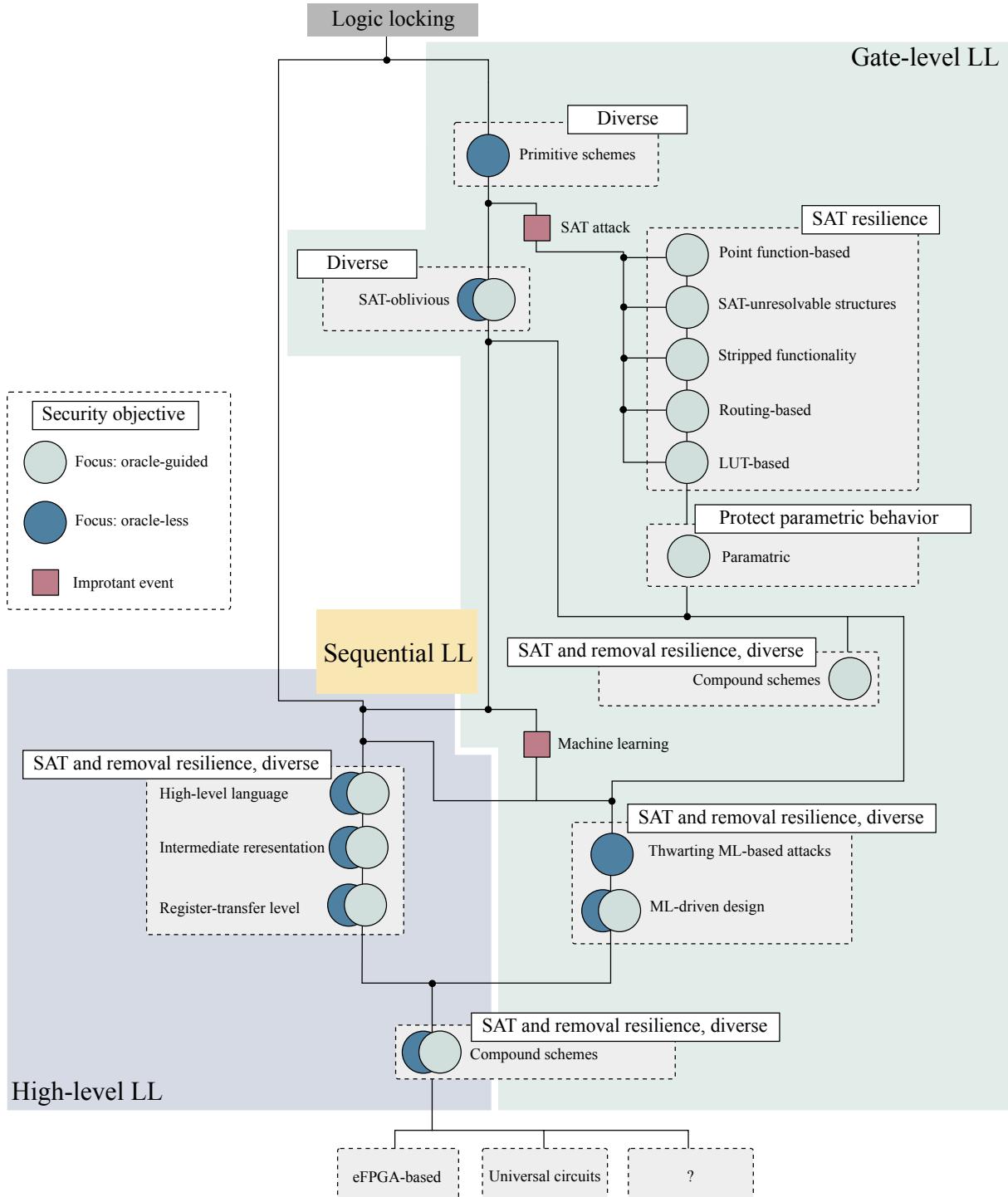

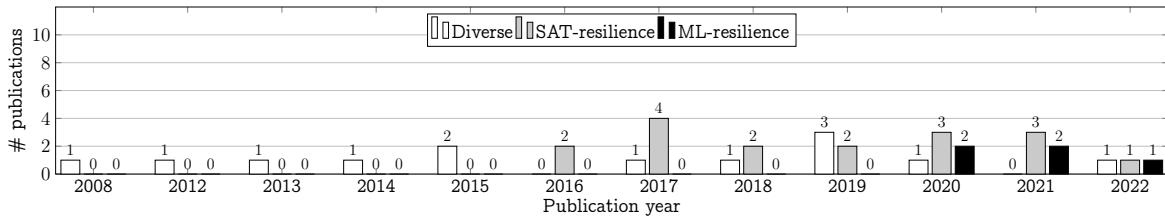

| 5.1.4. The Evolution of Logic Locking . . . . .                            | 51        |

| 5.1.4.1. Gate-Level LL . . . . .                                           | 51        |

| 5.1.4.2. High-Level LL . . . . .                                           | 53        |

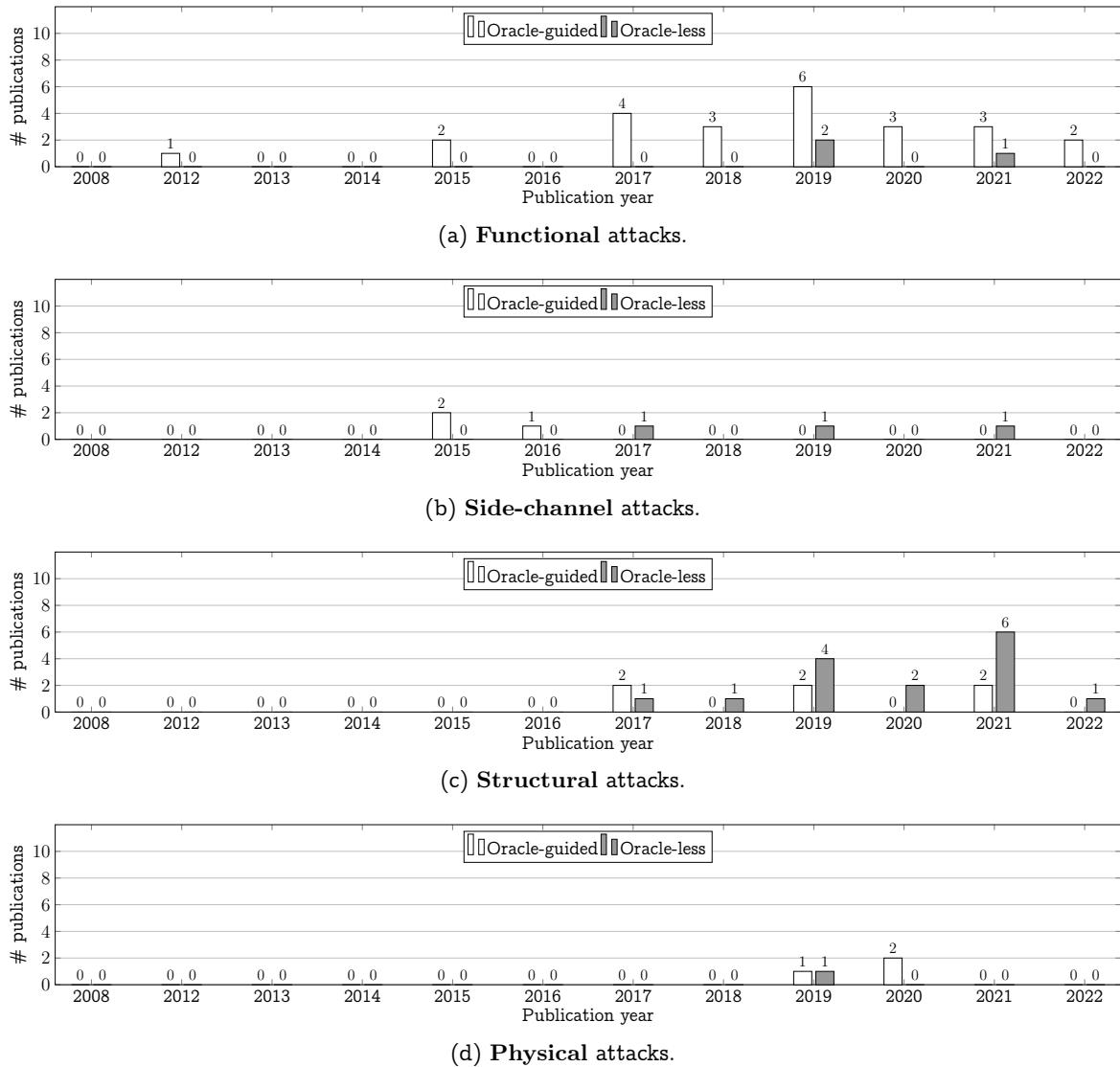

| 5.1.4.3. Attacks on Logic Locking . . . . .                                | 53        |

| 5.1.4.4. Fundamental Problems . . . . .                                    | 54        |

| 5.1.4.5. Current Trends . . . . .                                          | 55        |

| 5.2. Functional Filler Cells . . . . .                                     | 57        |

| 5.3. Split Manufacturing . . . . .                                         | 58        |

| 5.4. Layout Camouflaging . . . . .                                         | 58        |

| 5.5. Comparison of Design-for-Trust Techniques . . . . .                   | 59        |

| 5.6. Open Challenges . . . . .                                             | 59        |

| <b>6. Applicability of Detection and Protection Methods to the Asset</b>   | <b>60</b> |

| 6.1. Detection Techniques . . . . .                                        | 60        |

| 6.2. Protection Techniques . . . . .                                       | 62        |

| 6.3. Open Challenges . . . . .                                             | 62        |

| <b>III. WP3: Formal Security Guarantees, Auditability and Trust Models</b> | <b>63</b> |

| <b>7. Requirements for Formal Guarantees</b>                               | <b>65</b> |

| 7.1. A Complete Formal Description of the Asset . . . . .                  | 65        |

| 7.2. A Formal Description of the Protection or Detection Scheme . . . . .  | 66        |

---

|                                                                                      |           |

|--------------------------------------------------------------------------------------|-----------|

| 7.3. A Formal Proof of the Success of the Defense Against Hardware Trojans . . . . . | 66        |

| 7.3.1. Detection mechanisms . . . . .                                                | 66        |

| 7.3.2. Protection Mechanisms . . . . .                                               | 66        |

| <b>8. Possible Formal Security Guarantees for the Hardware Supply Chain</b>          | <b>68</b> |

| 8.1. Detection Mechanisms . . . . .                                                  | 68        |

| 8.1.1. Formal Methods . . . . .                                                      | 68        |

| 8.1.2. Other methods . . . . .                                                       | 69        |

| 8.2. Protection Mechanisms . . . . .                                                 | 69        |

| 8.3. Open Challenges . . . . .                                                       | 69        |

| <b>IV. WP4: Research Gaps and Recommendations</b>                                    | <b>70</b> |

| <b>9. List of Research Needs</b>                                                     | <b>72</b> |

| 9.1. Goal: Formal Security Guarantees . . . . .                                      | 72        |

| 9.2. Goal: Best-Effort Security . . . . .                                            | 73        |

| <b>10. Recommendation for Action</b>                                                 | <b>75</b> |

| 10.1. Cost Estimation . . . . .                                                      | 75        |

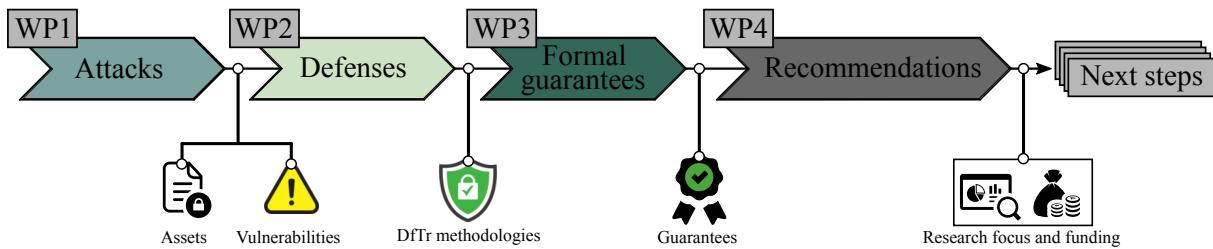

Figure 1.: Study workflow and concept.

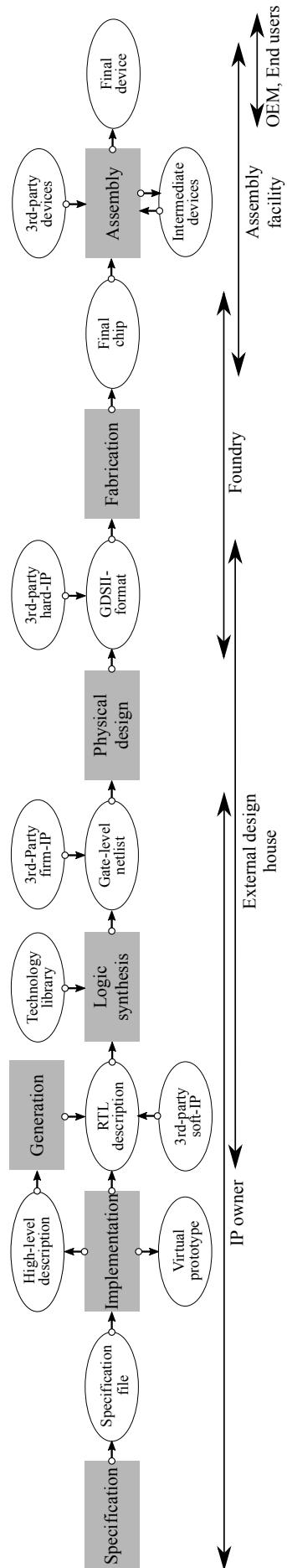

The contemporary Integrated Circuit (IC) supply chain follows a horizontal business model in which Intellectual Property (IP) owners rely on the involvement of external design houses and untrusted, off-site foundries. This mode of operation accommodates the need for a short time to market and reduces design and production costs. However, the inclusion of third parties has led to the rise of serious security and trust concerns throughout the IC supply chain, including IP piracy, IC counterfeiting, and malicious circuit modifications known as Hardware Trojans (HTs) [1].

In the last decades, hardware Trojans have been identified as a potential source of severe security vulnerabilities [2]. These malicious circuit modifications can be utilized to exploit, manipulate, and control electronic systems through judiciously inserted hardware backdoors. HTs can potentially lead to a wide range of attacks, including information leakage, denial of service, and reliability reduction, among others. As digital hardware plays a major role in all sectors of the modern age, HTs can incur significant damage and have dangerous consequences in the context of telecommunications, automotive electronics, medical devices, financial infrastructures, and military systems—just to name a few. Even though HTs have not been reported in the wild, the sheer fact that these tiny modifications can be implanted into hardware even with basic tooling [3] offers a potent motivation to design security mechanisms.

In the last decades, many efforts have been invested in exploring, implementing, and testing various methodologies to ensure trustworthiness throughout the IC supply chain. For example, the United States Defense Advanced Research Project Agency (DARPA) has issued multiple funding programs to support trustworthy electronics research and development, including the IRIS [4], TRUST [5], and SHIELD [6] program, among others. The potential of this issue has also been recognized within Germany. The German Federal Ministry of Education and Research (BMBF) has issued a funding program for 2021–2024 to tackle the challenges of trustworthy microelectronics for Germany and Europe [7; 8]. Unfortunately, to this day, a formal process of ensuring the trustworthiness of hardware across the IC supply chain has not been defined. Therefore, within this study, we evaluate existing protection mechanisms to define the required *focus and effort of future research challenges* to guarantee secure hardware throughout the supply chain.

This study follows the overall concept presented in Figure 1, consisting of four Work Packages (WPs). The first WP concerns the identification of the asset, its different formats, and its interaction with potential vulnerabilities throughout the Hardware (HW) supply chain. Hereby, we focus on the *point of contact* between the asset on different abstraction levels and untrusted parties or their tooling to gather a set of possible vulnerabilities. Within WP1, we further analyze the specific scenario of the untrusted foundry as the common denominator for most IP owners who have to operate fabless due to cost reasons.

WP2 focuses on the analysis of state-of-the-art protection and detection mechanisms w.r.t. malicious modifications at different supply-chain stages and HW abstraction levels. These so-called Design-for-Trust (DfTr) methodologies are further evaluated for their applicability for securing the critical asset from WP1.

In the next step, within WP3, we focus on possible formal guarantees of the DfTr methodologies identified in WP2. The existing guarantees are further extended with an analysis of the requirements necessary to enable an end-to-end procedure to formally secure the identified asset throughout the supply chain.

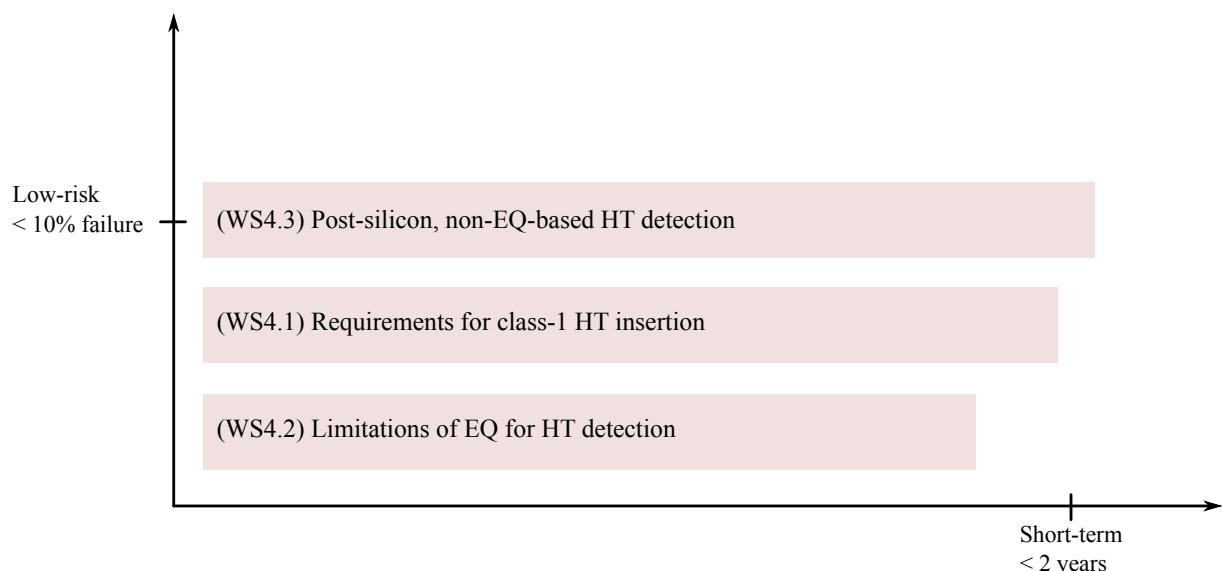

Finally, based on the study from the previous work packages, in WP4, we compile a list of relevant research challenges that aim to enable a formally verified and trustworthy hardware supply chain. The challenges are weighted w.r.t. the work complexity, applicability, and relevance. The research recommendation is presented alongside time estimations<sup>1</sup>.

---

<sup>1</sup> Note that the recommendations are based on possible challenges that might be addressed within the frame of 10 to 15 years.

Part I.

## WP1: Attacks Enabled by Malicious HW Manipulations

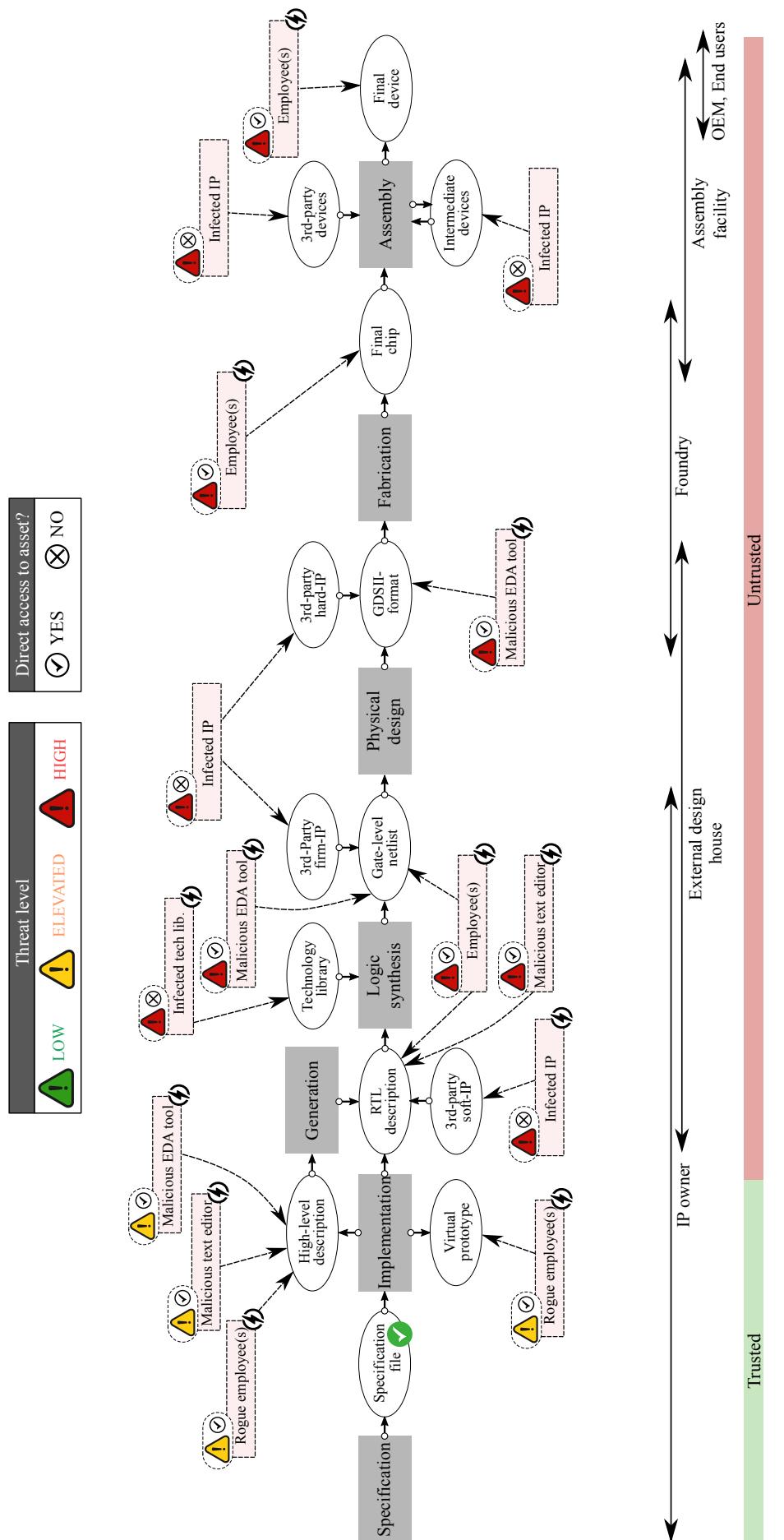

Part I of this study focuses on the mechanics of the electronics supply chain and its possible attack vectors. For this purpose, the entire supply chain is described to allow for a detailed inspection of every stage. The asset that requires protection is identified throughout the supply chain. For the security analysis, we build upon the *zero-trust* model to avoid overlooking any possible vulnerabilities [9]. To document the vulnerabilities, we analyze how the asset comes into contact with third-party Intellectual Properties (IPs), tools, and entities. Thus, every *contact point* between the asset and untrusted parties is regarded as a vulnerability.

Chapter 1 illustrates the electronics supply chain. The legitimate (trusted) IP takes many forms throughout the chain. Thus, the asset is represented for every stage of the supply chain in its current format.

Chapter 2 depicts every point of contact between the different representations of the asset and a third party, or their tooling and IP. The points describe the vulnerabilities and allow the identification of the attack vectors and their respective threat level. Hereby, a special focus is given to malicious design modifications known as hardware Trojans.

In Chapter 3, a specific focus is laid on untrustworthy external design houses and foundries as the business backbone of many IP owners. This deep reliance on outsourcing sensitive assets to third parties for design and manufacturing is marked by a loss of control and assurance thereof, thus introducing a major window of vulnerability that requires more attention.

# 1. Classification of Critical Assets

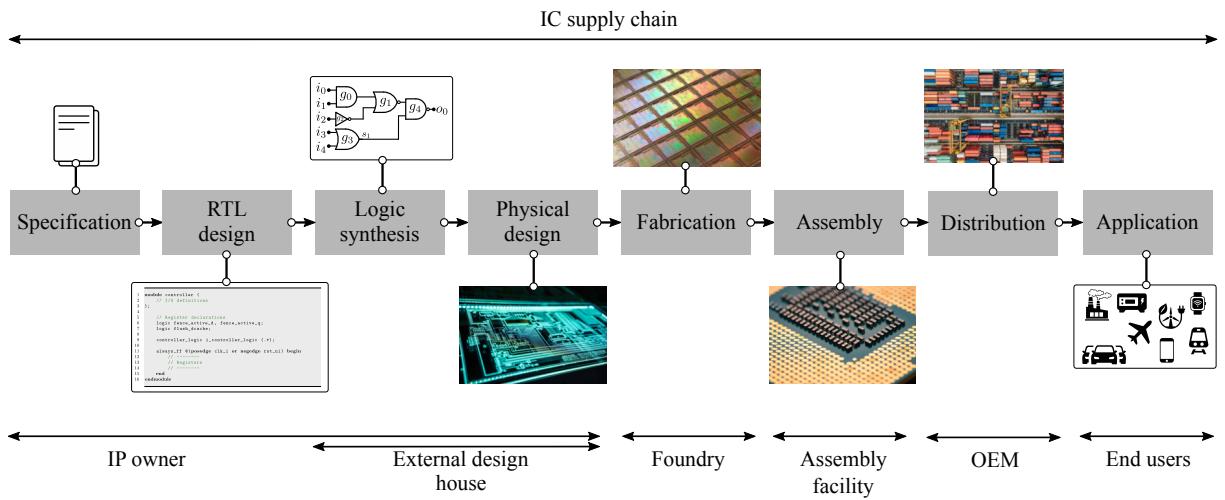

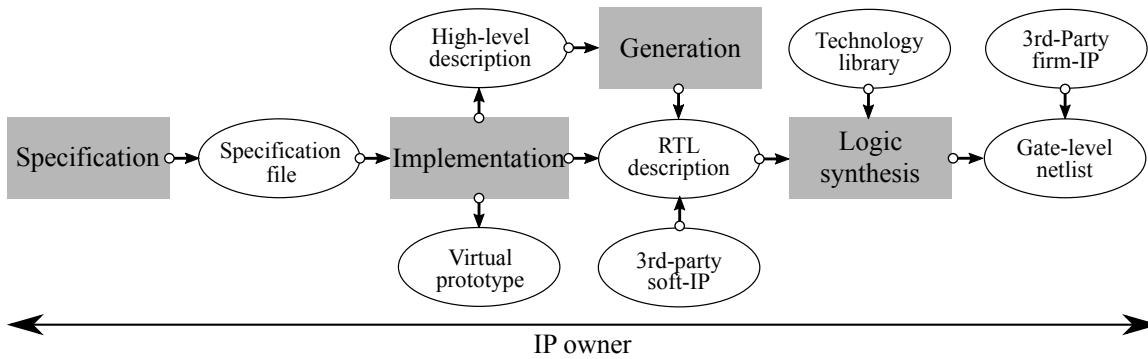

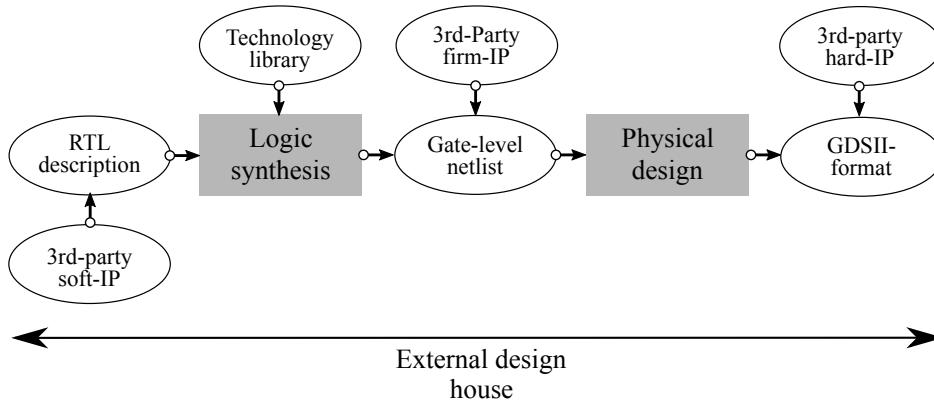

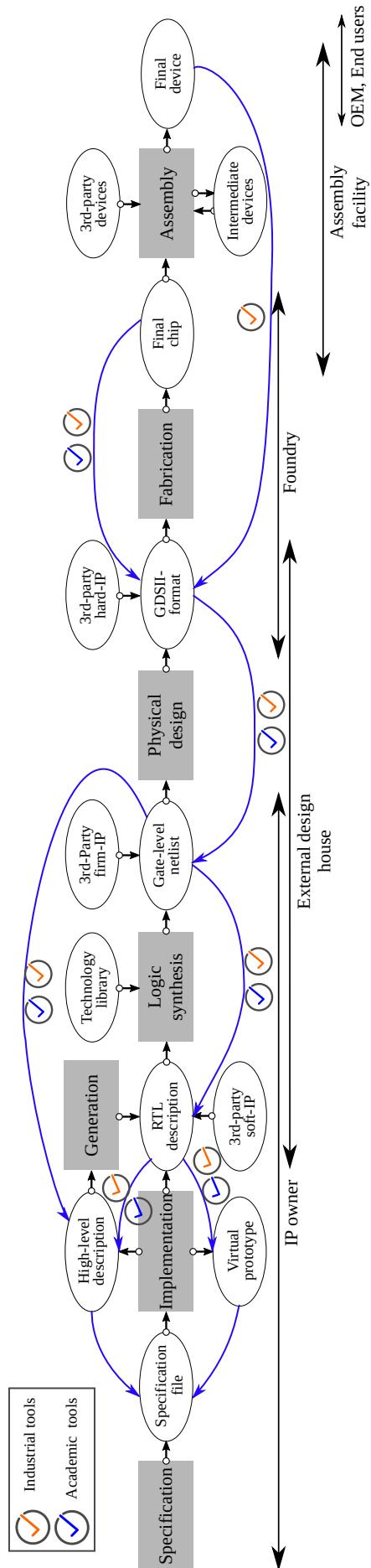

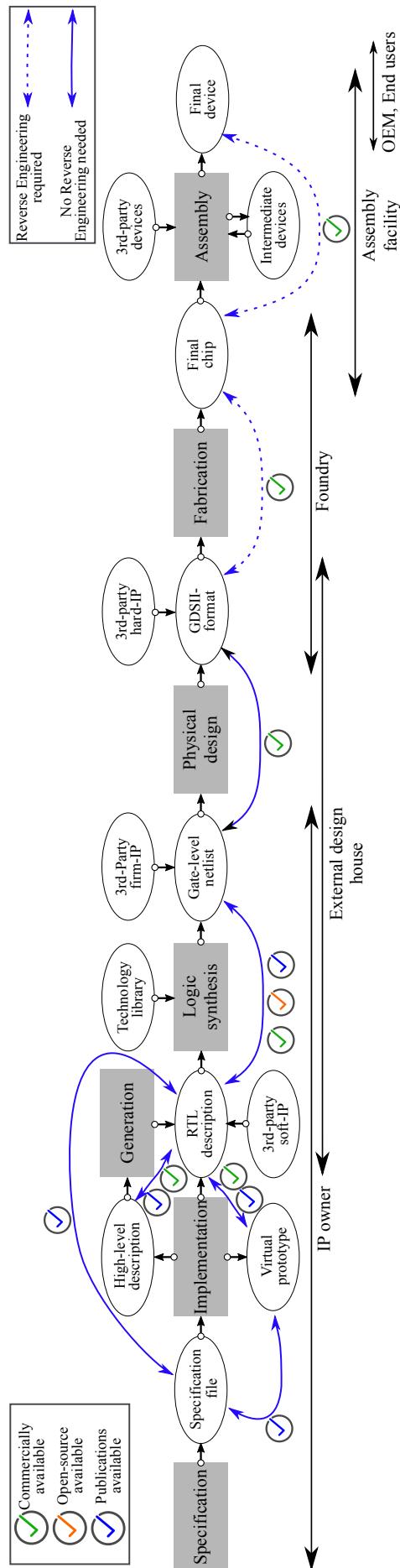

In this study, we focus solely on the hardware design—the IP—as the asset. This chapter depicts the electronics supply chain (Fig. 1.1) and the different formats of the asset during every link in the chain [10; 11].

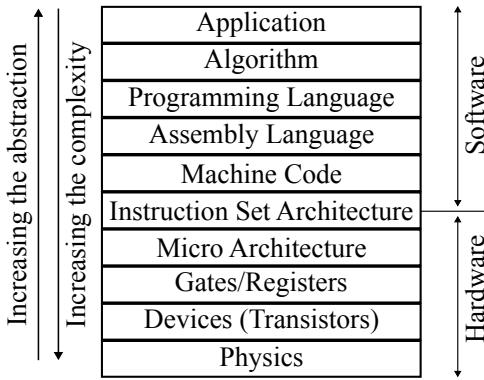

Figure 1.2.: Different hardware abstraction layers.

results in a more complex debug environment. Thus, an increasing number of design houses implement their designs in languages on higher abstraction levels. This ranges from software application languages, such as C (compiled to RTL via high-level synthesis [13]) to architecture description languages such as nML [14] that can be utilized to generate RTL automatically. Many commercial and open-source tools exist to process descriptions on higher abstraction levels to generate RTL [15]. Additional novel HW description languages include Chisel [16] and Bluespec [17], which can be used to generate Verilog.

Furthermore, modern HW designers use Virtual Prototypes (VPs) to simulate their design and enable early development of software for the intended HW. Some tools allow a generation of RTL code from the VP descriptions, such as SystemC [13]. But many designers implement the VP next to the hardware design.

Some components of the final RTL description are not designed in-house but are bought from third-party vendors. A third-party HW description on RTL is called soft IP. The additional RTL code is connected to the in-house design concluding the work on this abstraction level.

Once the RTL code is finalized, it needs to be transformed to a layout [18]. The resulting GDSII description is required by a foundry to manufacture the chip. This is done in two steps. First, logic synthesis is used to generate the gate-level netlist from the RTL description. This can be done using modern Electronic Design Automation (EDA) tools, such as Synopsys Design Compiler [19]. Second, the gate-level netlists is further processed via placement and routing to generate a spatial description of the HW—the so-called layout. Some IP owners do this process in-house, while others transmit their RTL design description to an external design house, where they conduct the logic synthesis as well as the placement and routing process. In this study, we will cover both scenarios, a supply chain with and without an external design house.

Table 1.1 and Figure 1.3 illustrate the different forms of the asset in the hands of the IP owner.

## 1.2. External Design House

An external design house can be the first third party to have full direct access to the IP. The designer gives the design house access to the HW description in the form of the gate-level netlist or the RTL description. The external designers are responsible for processing the description to enable the manufacturing by a foundry, resulting in a functional, in-silicon chip.

| Description              | Format                                        | Abstraction level       |

|--------------------------|-----------------------------------------------|-------------------------|

| Specification            | Text file or piece of paper                   | Specification           |

| Virtual prototype        | Text file (SystemC, ...)                      | System level            |

| Architecture description | Text file (nML, Bluespec, Chisel,...)         | Architecture level      |

| RTL design               | Text file (Verilog, VHDL, SystemVerilog, ...) | Register-Transfer level |

| Gate-level netlist       | Text file (Verilog)                           | Gate-level              |

Table 1.1.: List of assets in the hands of the IP owner.

Figure 1.3.: The asset changing format in the hands of the IP owner.

In case the external designers process the RTL description, logic synthesis needs to be done, mapping the generic description onto a technology library. The resulting gate-level netlist can be used to estimate the clock speed and area of the resulting chip.

The netlist is technology-dependent but does not give any information about the physical location of every gate. Placement and routing are conducted by the design house using modern EDA tools, typically by Cadence or Synopsys. This step ensures the generation of a 3-dimensional description defining the placement and connectivity of every single transistor in the chip. Additionally, the clock tree needs to be designed with the intent that the clock signal reaches every design component in time. The final design in GDSII format (=the layout) can be forwarded to the foundry for manufacturing.

An additional service that is offered by most design houses is the implementation of the Design for Test (DfT) logic. Further wiring and registers are added to the design to allow the testing of the internal state of the design. Scan-chains offer easy access to the internal signal state of the architecture at runtime. The signals are accessible via an additional interface, often JTAG, to allow the analysis of the architecture's behavior on new software or input patterns. The interface is often encrypted or destroyed after the chip is tested to avoid the leakage of sensitive data after releasing the final chip [20].

Table 1.2 and Figure 1.4 illustrate the different formats of the asset in the hands of the external design house.

| Description        | Format                                        | Abstraction level       |

|--------------------|-----------------------------------------------|-------------------------|

| RTL design         | Text file (Verilog, VHDL, SystemVerilog, ...) | Register-transfer level |

| Gate level netlist | Text file (Verilog)                           | Gate Level              |

| Layout             | GDSII Design                                  | Layout level            |

Table 1.2.: List of asset formats in the hands of the external design house.

Figure 1.4.: The asset changing format within the hands of the external design house.

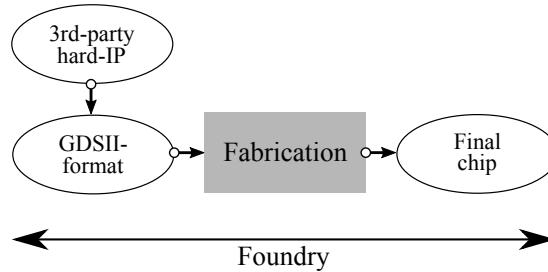

### 1.3. Foundry

Many modern designers cannot maintain their own foundry. Therefore, the manufacturing process is outsourced to a third party. The foundry receives the layout of the design and returns a batch of manufactured chips.

The technology library chosen for the logic synthesis needs to represent a technology that can be provided by the foundry, as the manufacturing equipment must match the exact specifications of the underlying technology. In many cases, the foundry also provides the packaging of the chip, allowing other parties to implement the IP on a circuit board, e.g., a Printed Circuit Board (PCB). The ports are connected to pins, and the chip is packaged for protection against physical damage.

Table 1.3 and Figure 1.5 illustrate the different formats of the asset in the hands of the foundry.

| Description   | Format                                                   | Abstraction level |

|---------------|----------------------------------------------------------|-------------------|

| Layout        | Text file (GDSII format)                                 | Layout            |

| Final chip    | Physical design, not combined into a device yet          | Physical layer    |

| Packaged chip | Physical design - packaged - allows integration into PCB | Physical layer    |

Table 1.3.: List of asset formats in the hands of the foundry.

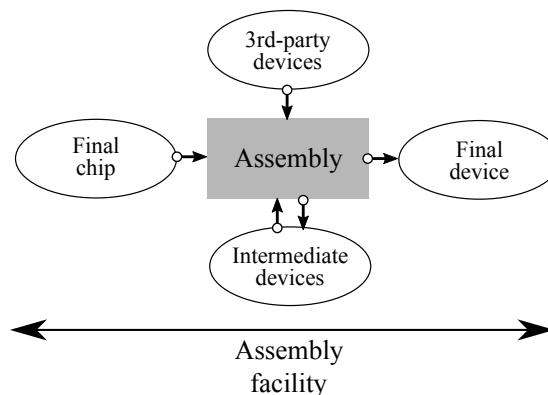

### 1.4. Assembly

The assembly step in the supply chain can include multiple entities. The assembly constructs multiple components to fit a certain application. For a single chip batch, this can lead to either the same product or diversified products.

Figure 1.5.: The asset changing format within the hands of the foundry.

A common strategy for assembling the final product is the modular system. Several smaller components are assembled to form intermediate products, which are further assembled with other intermediate products to form a larger module or the final product. Multiple production entities may be involved in developing the individual modules. In this context, the client can receive a packaged chip of the owner's IP or an unpackaged version, depending on how the different components are assembled.

Table 1.4 and Figure 1.6 illustrate the different formats of the asset in the hands of the assembly facility.

| Description         | Format                                                    | Abstraction level |

|---------------------|-----------------------------------------------------------|-------------------|

| Final chip          | Physical design, not combined into a device yet           | Physical layer    |

| Intermediate device | Physical design, combined with some additional components | Physical layer    |

| Final device        | Physical design, packaged                                 | Physical layer    |

Table 1.4.: List of asset formats in the hands of the assembly facility.

Figure 1.6.: The asset changing format within the hand of the assembly facility.

## 1.5. OEM

After all components are assembled to form the final product, the chips are distributed by either the IP owner or an Original Equipment Manufacturer (OEM) procurement is utilized. The

product can be sold to an OEM, which distributes the product to be rebranded and used in other companies' products.

Table 1.5 and Figure 1.7 illustrate the different formats of the asset in the hands of the OEM.

| Description  | Format                    | Abstraction level |

|--------------|---------------------------|-------------------|

| Final device | Physical design, packaged | Physical layer    |

Table 1.5.: List of asset formats in the hands of the OEM.

Figure 1.7.: The asset changing format within the hands of the OEM.

## 1.6. End Users

The final design, which includes the asset, is sold to the end user.

Table 1.6 and Figure 1.7 illustrate the different formats of the asset in the hands of the end user.

| Description  | Format                                                    | Abstraction level |

|--------------|-----------------------------------------------------------|-------------------|

| Final device | Physical design, packaged, combined with other components | Physical layer    |

Table 1.6.: List of asset formats in the hands of the end user.

The final asset chain that corresponds to the supply chain in Figure 1.1 is illustrated in Figure 1.8.

Figure 1.8.: The asset changing format within the hands of the end user.

## 2. Electronics Supply Chain Threats: Hardware Manipulations

The electronics supply chain operates in a horizontal fashion, optimizing for short time-to-market deadlines and cost reduction. These objectives, however, force legitimate IP owners to rely on the inclusion of a plethora of external entities, as well as closed-source, third-party EDA tools. This complexity and distributed nature of the supply chain have led to a profusion of security vulnerabilities due to one simple reason—*unverifiable assurance of trust* between the involved parties. One of the most critical security threats enabled by this absence of verifiability are malicious design modifications known as Hardware Trojans (HTs). HTs have become a driving force for security research for more than a decade [2]. Unfortunately, the issue of HTs is far from resolved.

To further analyze the background and source of HTs<sup>1</sup>, this chapter takes a closer look at state of the art in HT design, classification, and implementation in Section 2.1. Possible attack models that lead to HT insertion are analyzed in Section 2.2. A threat evaluation is performed through the mentioned analysis, with a final conclusion in Section 2.3. Finally, open challenges are summarized in Section 2.4. *Note that we consider any form of malicious manipulation, regardless of whether logic is removed, bypassed, or added within a design, as a HT.*

### 2.1. Hardware Trojans

Hardware Trojans can be defined as malicious, intentional, and stealthy modifications of integrated circuits during the entire HW supply chain [21]. The malicious behavior can be embodied in the form of information leakage, power dissipation, denial of service, performance degradation, or, more generally, in a behavior that is not originally intended. The modification must be intentional; otherwise, the Trojan is equivalent to a random fault. The implementation of Trojans is assumed to be stealthy to enable the modification to pass through any form of tests and security checks, thus allowing the Trojan to remain dormant in the chip until activation.

#### 2.1.1. Trojan Components

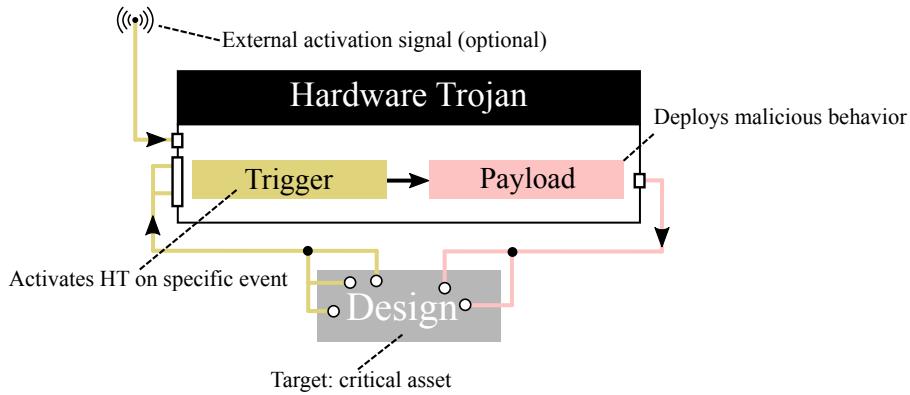

The research community has defined the following HT components: trigger and payload [22; 23; 24]. A visualization is given in Figure 2.1. The *trigger* mechanism activates the payload on a certain event. This event can be arbitrarily complex, including external signals (e.g., through a signal captured by an antenna), specific input values or a series of input patterns, specific circuit states, number of cycles, sensor values, and others. The *payload* is the manifestation of the malicious behavior that results in the intended attack.

---

<sup>1</sup> Within the scope of this study, we sometimes refer to hardware Trojans as "Trojans".

Figure 2.1.: Hardware Trojan components.

The implementation variety of the trigger and the payload has, in principle, no limits. To make things worse, HTs can be injected into the target design at any stage within the HW supply chain. Thus, HTs create a vast attack landscape that still remains an open problem.

### 2.1.2. Classifications

The complexity of the HT-enabled attack landscape has triggered efforts to create a classification of HT implementations, with the intention of easing the path toward potential detection or prevention methods by better understanding how Trojans could be implemented. In the following, we discuss existing classification concepts. Note that most classification systems are evolving in time, as researchers identify novel ways of injecting and designing Trojans. Hence, the following data captures the state of classifications in the referenced publications.

#### 2.1.2.1. Physical, Activation, and Action Characteristics

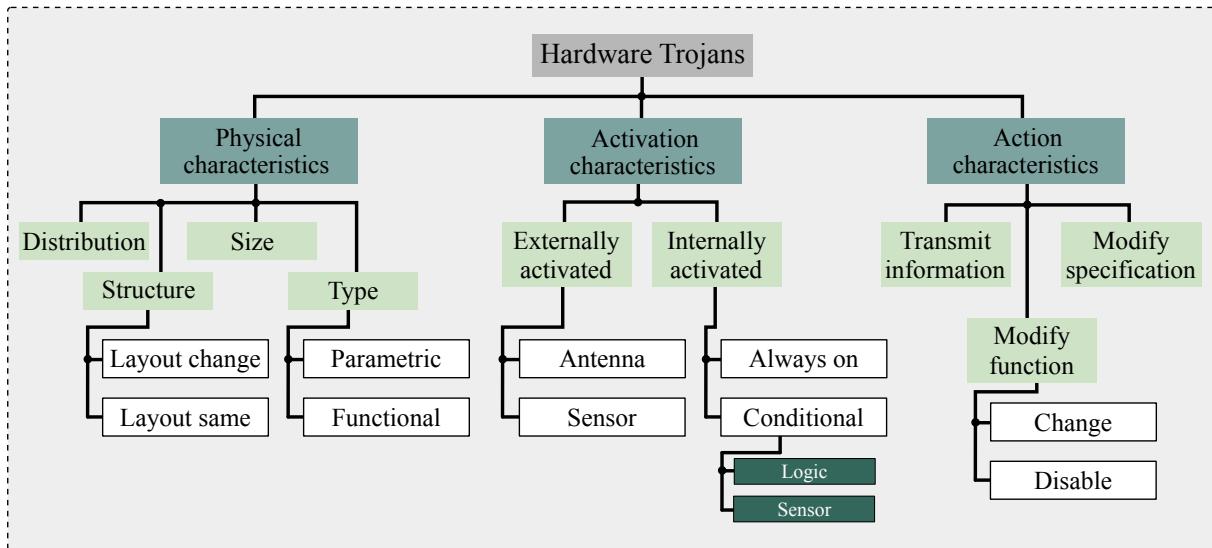

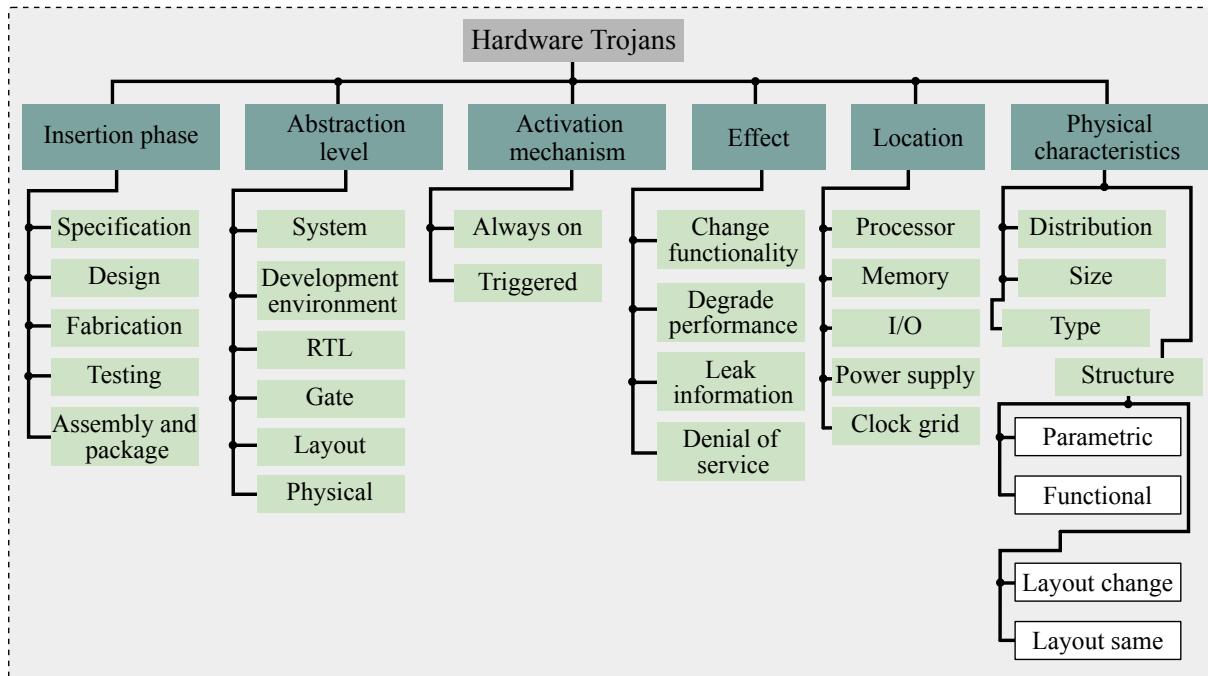

An early attempt at classifying hardware Trojans was presented in [25; 26] with the objective of facilitating the proper evaluation of the effectiveness of HT detection methods. Here, HTs are decomposed based on three criteria: physical, activation, and action characteristics. This classification is shown in Figure 2.2.

The physical class describes different hardware implementations of Trojans, including the distribution, structure, size, and type. The distribution refers to the location of the Trojan's implementation within the chip's layout. The structure category captures the case when the layout must be regenerated due to the injected HT; thus, either a layout change exists or not. The size category describes the number of components in the chip that have been added, changed, or deleted due to the HT. Finally, the type category segregates Trojans into the functional and parametric classes. The former includes Trojans that are manifested through the physical addition or deletion of transistors or gates. The latter describes Trojans that rely on modifications to existing wires, gates, and logic.

The second decomposition accounts for the activation characteristics that trigger the HT's malicious behavior. The characteristics are separated into externally and internally activated Trojans. External activation can be manifested in the form of an antenna that receives a certain trigger signal or specific sensor values used to interact with the chip's environment. Internally activated Trojans capture two subclasses: always-on and conditional HTs. Always-on HTs are

Figure 2.2.: Hardware Trojan classification based on physical, activation, and action characteristics.

continuously active and can corrupt the chip's functionality at any time. Conditional Trojans, on the other hand, activate only on the occurrence of a specific event, such as specific logic or sensor values.

The third class captures the action characteristics of Trojans. Note that "action" can be considered as the payload—as discussed in Section 2.1.1. This class targets three different behavioral traits: transmission of information, functional modification, and modification of the specification. The transmit-information class captures Trojans that enable or facilitate the transmission of secret keys or, in general, data to an attacker. The modification-of-function class describes Trojans that affect the chip's intended functionality by adding, removing, or bypassing logic. Finally, the modify-specification class includes Trojans that target the change of parametric values of the chip, such as the power or delay characteristics.

### 2.1.2.2. Activation Mechanism and Effect

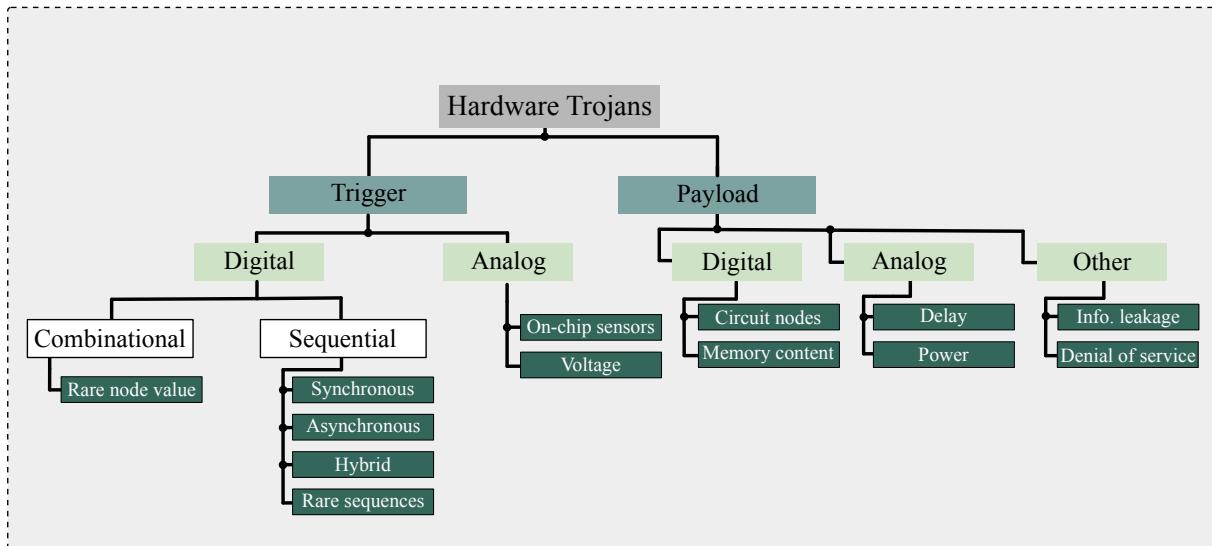

A high-level classification of hardware Trojans was presented in [24]. The classification segregates Trojan types based on variations in activation mechanisms and the payloads' effect. The classification is presented in Figure 2.3.

The trigger classifies HTs into analog and digital Trojans. The former captures activation mechanisms through analog computing, such as device aging and temperature variations. The latter represents Trojans that are activated by a Boolean function. Trojans triggered by analog effects are considered to attack process steps that compromise the reliability of the target chips. Examples include specific values of on-chip sensors or voltage variations. Digitally triggered Trojans are further classified as combinational and sequential. Combinational HTs listen to specific in-circuit values that do not require the support of multiple states. An example are one-time rare inputs or node values<sup>2</sup>. Sequential Trojans rely on a certain combination or value of states, such as a certain value of a counter after a selected number of cycles.

<sup>2</sup> A node value is the value of the output wire of a node (gate) in the circuit.

Figure 2.3.: Hardware Trojan classification based on trigger and payload mechanisms.

The payload mechanism segregates Trojans based on the type of effect the Trojans have on the infected circuit operation, including digital, analog, and other responses. Digital payloads can, for example, change the value of certain signals within the circuit or the system's memory. Analog payloads influence the power and delay characteristics of the target chip. Other payloads might result in information leakage by creating additional paths between critical (secret) keys or data and primary outputs, or block further chip operation, thus leading to a Denial of Service (DoS) attack.

#### 2.1.2.3. A Comprehensive Classification

A comprehensive classification of hardware Trojans was proposed and refined in [27; 10]. The classification is visualized in Figure 2.4. This classification was developed to enable the comparison of HT-detection methods. Moreover, it was used as a guideline to compile the currently largest collection of online-available "trust benchmarks"<sup>3</sup>—a set of Trojan-infected hardware benchmarks. This classification looks at the entire spectrum of Trojan types spanning from the supply-chain phase in which the Trojan is inserted to the physical characteristics of the Trojans' implementation.

At the highest level, the classification starts with Trojans that are inserted in different supply-chain stages, thus covering the specification, design, fabrication, testing, and assembly and packaging phase. Next, the abstraction level at which the Trojan is injected is considered. This includes Trojans designed and inserted at the system level down to the physical layout. In the following step, Trojans are segregated based on the activation mechanisms. Here, similar to the classification in Section 2.1.2.1, the trigger mechanism can be always-on or conditionally triggered by a selected event. Next, the Trojan effect is used as a separation criterion. Thus, Trojans are classified based on the manifestation of their payload in the form of a functional circuit change, performance degradation, information leakage, and denial of service. The location criterion describes the exact location, such as a design module, where the HT is inserted. Finally, Trojans are distinguished based on their physical characteristics in the same manner as in Section 2.1.2.1.

<sup>3</sup> The benchmarks are freely available here: <https://www.trust-hub.org/>

Figure 2.4.: A comprehensive hardware Trojan classification.

#### 2.1.2.4. Reverse-Engineering-Based Classification

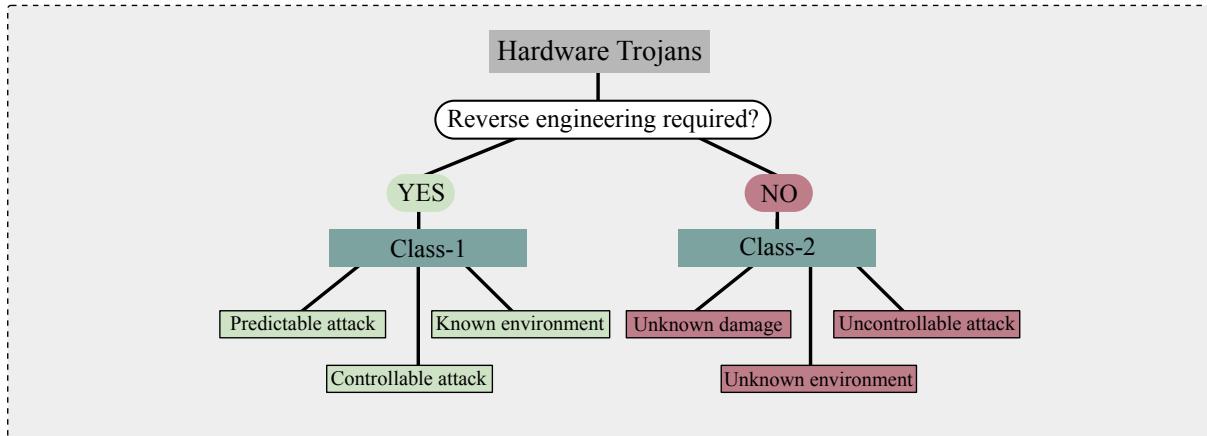

The previous classification systems offer detailed guidelines on how to describe, categorize, and evaluate hardware Trojans. Unfortunately, the classifications simply try to capture as many implementation features as possible, thereby speculating what traits HTs might have. Another downside of this descriptive classification approach is that it does not create any relation to defensive approaches: what does a Trojan class tell us about how we can protect against it? To answer this question and overcome the endless feature accumulation of Trojan types, a consolidated classification was presented in [28]. This classification system aims at separating all Trojans into two categories, Class-1 hardware Trojans (C1HTs) and Class-2 hardware Trojans (C2HTs), based on a single criterion—the requirement of Reverse Engineering (RE) for Trojan design and insertion. The consolidated system is shown in Figure 2.5.

C1HTs cover Trojans that are RE-dependent. Thus, the attacker must invest a certain effort to understand the target's (asset's) design specification (at an arbitrary level) to design and insert a design-specific hardware Trojan. Consequently, a C1HT allows for a *controllable* trigger leading to a *high-impact* attack in a *known* application environment. In a more simple model, C1HTs comprise all Trojans for which at least one design component—the trigger *or* the payload—is RE-dependent. An example of such a Trojan is a modification of the decoder of a RISC-V microarchitecture that filters out a specific sequence of (software) instructions and, upon triggering, leads to a complete stop of instruction execution, i.e., a DoS attack. Hereby, we assume that the attacker must identify the exact functionality of the asset (=processor), its specifications (=RISC-V instruction set), its microarchitectural design traits (=location of the decoder), and the application area (=e.g., control unit of a radar system). Evidently, this configuration can lead to disastrous attack vectors. Since a certain RE effort is required for the injection of class-1 Trojans, any form of protection mechanism that increases the RE effort might be used as a deterrent.

C2HTs includes Trojans that are RE-independent. Therefore, an attacker is able to insert this

Figure 2.5.: Hardware Trojan classification based on the reverse-engineering effort.

type of hardware Trojans into a design at any stage or abstraction level without any knowledge about the underlying asset. Consequently, C2HTs are malicious modifications for which both design components—the trigger and the payload—are RE-independent. As no RE effort is required for the design and insertion of a C2HT, it can always be inserted regardless of potential protection mechanisms. Nevertheless, such a Trojan might be of low impact, high detectability, result in random attacks, or by chance, might never be triggered. An example of a class-2 Trojan is an XOR gate that takes two inputs: a selection input and a random wire from the asset. When the selection bit is (in an arbitrary way) set to 1, the second input is inverted, thus injecting some form of faulty behavior into the circuit. Otherwise, no change is introduced. Evidently, such a Trojan can always be inserted into the design without any knowledge about the asset or its application domain. More details can be found in [22].

### 2.1.3. Example Trojan Implementations

As discussed in Section 1, a wide range of entities, tools, and third-party IP is involved in the design of a single chip. Moreover, the involved parties are often spread across multiple companies operating in different countries and continents. Alongside the endless and intricate implementation variations of HTs, the distributed nature of the supply chain makes it extremely hard to catch hardware Trojans in the wild. Thus, so far, no confirmed case of a "real world" HT is known. Moreover, the question is whether a company that detects an infected chip would publicly announce it? The infection might remain a secret to protect the company's business. Nevertheless, some alleged Trojans have been documented. One prominent example is described in the case of a Syrian radar system that failed to warn of an incoming airstrike. The failure was speculated to have been caused by HTs integrated into the defense systems [29; 30].

The academic examples, on the other hand, are abundant and reach across all previously discussed classifications [24; 31; 32; 33; 34; 10; 35; 36; 37], some of which have also been put into silicon for demonstration and measurements [38; 39]. Moreover, a recent study also demonstrated the automatic insertion of hardware Trojans into circuits by means of standard EDA development tools [3]. Note that a practically unlimited number of Trojan examples can be fabricated as Trojans are, in terms of implementation, not different from any other hardware circuit—one fundamental reason why it is so challenging to detect these alterations.

Table 2.1.: Threat levels for hardware Trojan insertion.

| Level    | Access format  | Direct access? | Access environment | Comment                                           |

|----------|----------------|----------------|--------------------|---------------------------------------------------|

| LOW      | Third-party IP | ✗              | Trusted            | HT only in external files.                        |

| HIGH     | Third-party IP | ✗              | Untrusted          | HT only in external files.                        |

| ELEVATED | EDA tool       | ✓              | Trusted            | HT insertion requires a high level of automation. |

| HIGH     | EDA tool       | ✓              | Untrusted          | HT insertion requires a high level of automation. |

| ELEVATED | Employee(s)    | ✓              | Trusted            | HT embedded in in-house environment.              |

| HIGH     | Employee(s)    | ✓              | Untrusted          | HT embedded in off-site environment.              |

## 2.2. Attack Models

This section takes a closer look at different attack models that are enabled by the *contact point* between the asset (the legitimate IP) and untrusted or external entities, tools, or third-party IPs. Hereby, we look at each stage of the supply chain individually. For each stage, we analyze what attack scenario is enabled by the available contact points. Every scenario is categorized by a *threat level*. The threat levels are further described in Section 2.2.1. An overview of all HT-based threats are shown in Figure 2.6.

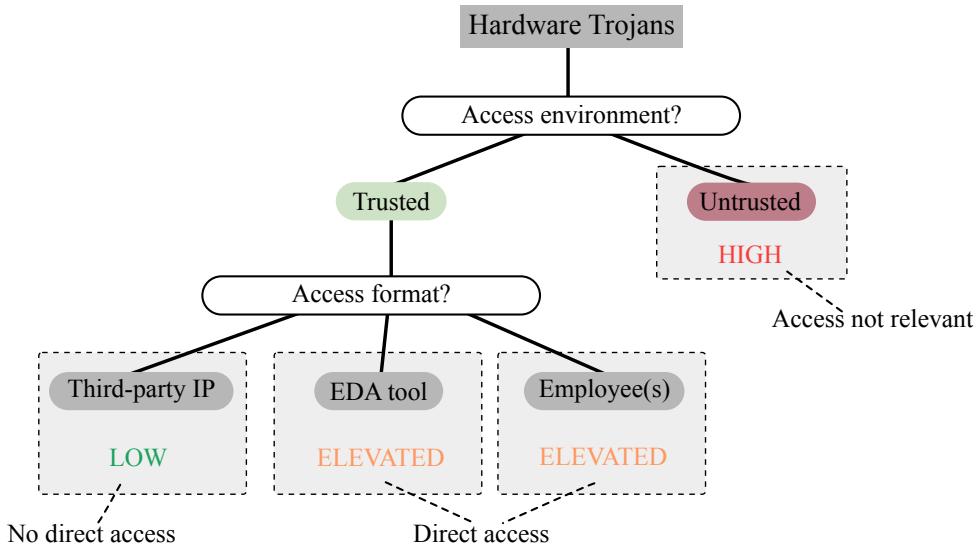

### 2.2.1. Threat Levels

The threat levels used in this study are listed in Table 2.1. The objective of the threat levels is to express the probability of an attack at a certain stage of the supply chain, regardless of its effort and impact. Two criteria define the threat level: the access format and environment. These criteria are defined as follows:

- **Access format:** The access format defines how the malicious entity gets access to the asset. The format includes third-party IP, EDA tools, and rogue employees.

- Third-party IP: The HT is embedded in a third-party IP. Thus, the HT can only influence the asset through externally included files.

- EDA tool: The EDA tool has complete access to the asset and inserts the HT.

- Employee: A malicious employee has complete access to the asset and inserts the HT.

- **Access environment:** The access environment includes two scenarios: trusted and untrusted. The former indicates that the HT is (willingly or unwillingly) inserted into the asset in an environment that is supposed to be trusted (e.g., in the case of the IP owner). The latter captures HT insertions in external, off-site environments that are considered untrusted.

Using the criteria, we can distinguish three threat levels that are mainly directed by the **access environment**. A visualization of the decision tree that determines the threat level is shown in Figure 2.7. If the attack takes place in an **untrusted** environment, every threat, regardless of its access format, is labeled with a **HIGH** threat level. The reason is that an untrusted environment has full and direct access to the asset.

If the attack takes place in a **trusted** environment, the threat level depends on the **access format**. If the HT is embedded in a third-party IP (=no direct access), it is marked with a **LOW** threat

Figure 2.6: Hardware Trojans in the electronics supply chain.

Figure 2.7.: Threat-levels decision tree.

level. If the access is direct, e.g., through a malicious EDA tool or rogue employees, the threat level is set to ELEVATED.

### 2.2.2. Hardware Trojans: Insertion Effort and Impact

Each scenario in the following sections is described with two additional parameters: effort ( $E$ ) and impact ( $I$ ).  $E$  captures the effort required to insert a design-specific hardware Trojan (=class-1 HT).  $I$  describes the potential impact of the hardware Trojan (=impact of the attack caused by a hardware Trojan). We estimate the effort and impact based on three variables:

- Environment type ( $\tau$ ): trusted or untrusted (see Section 2.2.1).

- Reverse engineering effort ( $\kappa$ ): the effort required to fully understand the target design in order to insert a design-specific (class-1) Trojan.

- Direct access ( $\delta$ ): the type of access to the target design (see Section 2.2.1).

The variable values are presented in Table 2.2. The effort depends on the type of environment

Table 2.2.: Effort and impact variables.

(a) Environment ( $\tau$ ). (b) RE effort ( $\kappa$ ). (c) Direct access ( $\delta$ ).

| Environment type | Value      | RE effort     | Value        | Direct access | Value        |

|------------------|------------|---------------|--------------|---------------|--------------|

| Trusted          | $\tau = 1$ | RTL or higher | $\kappa = 1$ | No            | $\delta = 1$ |

| Untrusted        | $\tau = 2$ | Gate level    | $\kappa = 2$ | Yes           | $\delta = 2$ |

|                  |            | Layout level  | $\kappa = 3$ |               |              |

|                  |            | Chip level    | $\kappa = 4$ |               |              |

|                  |            | Device level  | $\kappa = 5$ |               |              |

and reverse-engineering effort:

$$E = \frac{\kappa}{\tau}. \quad (2.1)$$

An untrusted environment facilitates the insertion of a hardware Trojan (=lower effort) as the insertion takes place in an isolated, external location. A trusted environment increases the effort, as a malicious behavior of an attacker might be more detectable, thus constraining the actions of the adversary. Moreover, the effort decreases with higher abstraction levels. For example, it stands to reason that the effort to insert a design-specific Trojan is lower on RTL than on layout level, as less reverse-engineering must be performed to understand the target design.

The impact of the Trojan depends on the environment and the access to the target design:

$$I = \tau \cdot \delta. \quad (2.2)$$

The impact is higher in untrusted environments, because the malicious party can move more freely. Furthermore, having direct access to the target design allows for a more design-specific implementation of the Trojan, thus resulting in a (potentially) higher impact.

Using the definitions above, we can look at corner cases to better understand the variables:

- Highest effort: trusted environment and layout level (no known example).

- Lowest effort: untrusted environment and RTL (or higher) level (external design house, RTL).

- Highest impact: untrusted environment and direct access (external design house/foundry, employees).

- Lowest impact: trusted environment and no direct access (IP owner, third-party IP).

### 2.2.3. IP Owner

The IP owner is considered a trusted environment. The possible attack vectors in this stage are listed in Table 2.3. The specification is assumed to be trusted and not affected by malicious modifications. All attack vectors with direct access to the asset are labeled with an **ELEVATED** threat level. The reason is that even though direct access is provided, the attack takes place in a trusted environment in which (almost) all employees are supposed to be trusted. Thus, even malicious employee(s) or EDA tools might be less effective in this environment. Third-party IPs are labeled as **LOW** as no direct access to the asset is provided.

### 2.2.4. External Design House

The external design house is considered an untrusted environment. The attack vectors are listed in Table 2.4. All contact points of the asset with third-party IP, tools, and employees are labeled as **HIGH** threats since the untrusted party has full and uncontrolled access to the asset.

### 2.2.5. Foundry

The foundry is considered an untrusted environment. The attack vectors are listed in Table 2.5. All contact points of the asset with third-party IP, tools, and employees are labeled as **HIGH** threats

Table 2.3.: Attack model: IP owner.

| Asset               | Untrusted entity                    | Example scenario(s)                                       | Threat level | Direct access | E | I |

|---------------------|-------------------------------------|-----------------------------------------------------------|--------------|---------------|---|---|

| Virtual prototype   | Rogue employee(s)                   | Hiding faulty behavior of trigger software.               | LOW          | ✗             | 1 | 1 |

| Architectural desc. | Rogue employee(s)                   | Manual inclusion of HT.                                   | ELEVATED     | ✓             | 1 | 2 |

| Architectural desc. | Malicious third-party text editor.  | Automatic insertion of HTs based on static code analysis. | ELEVATED     | ✓             | 1 | 2 |

| Architectural desc. | Malicious EDA tool: code generation | Automatic insertion of HTs based on static code analysis. | ELEVATED     | ✓             | 1 | 2 |

| RTL design          | Rogue employee                      | Manual inclusion of HT.                                   | ELEVATED     | ✓             | 1 | 2 |

| RTL design          | Malicious third-party text editor.  | Automatic insertion of HTs based on static code analysis. | ELEVATED     | ✓             | 1 | 2 |

| RTL design          | Infected third-party IP.            | Infected soft IP.                                         | LOW          | ✗             | 1 | 1 |

| Gate-level netlist  | Rogue employee(s)                   | Manual inclusion of HT.                                   | ELEVATED     | ✓             | 2 | 2 |

| Gate-level netlist  | Malicious EDA tool: logic synthesis | Automatic insertion of HTs based on static code analysis. | ELEVATED     | ✓             | 2 | 2 |

| Gate-level netlist  | Infected technology library         | HT hides in specific cells.                               | LOW          | ✗             | 2 | 1 |

| Gate-level netlist  | Infected third-party IP             | Infected firm IP.                                         | LOW          | ✗             | 2 | 1 |

Table 2.4.: Attack model: External design house.

| Asset              | Untrusted entity                    | Example scenario(s)                                       | Threat level | Direct access | E   | I |

|--------------------|-------------------------------------|-----------------------------------------------------------|--------------|---------------|-----|---|

| RTL design         | Employee(s)                         | Manual inclusion of HT.                                   | HIGH         | ✓             | 0.5 | 4 |

| RTL design         | Malicious third-party text editor.  | Automatic insertion of HTs based on static code analysis. | HIGH         | ✓             | 0.5 | 4 |

| RTL design         | Infected third-party IP.            | Infected soft IP.                                         | HIGH         | ✗             | 0.5 | 2 |

| Gate-level netlist | Employee(s)                         | Manual inclusion of HT.                                   | HIGH         | ✓             | 1   | 4 |

| Gate-level netlist | Malicious EDA tool: logic synthesis | Automatic insertion of HTs based on static code analysis. | HIGH         | ✓             | 1   | 4 |

| Gate-level netlist | Infected technology library         | HT hides in specific cells.                               | HIGH         | ✗             | 1   | 2 |

| Gate-level netlist | Infected third-party IP             | Infected firm IP                                          | HIGH         | ✗             | 1   | 2 |

| Layout             | Infected third-party IP             | Infected hard IP.                                         | HIGH         | ✗             | 1.5 | 2 |

| Layout             | Malicious EDA tool: physical design | Automatic insertion of HTs based on netlist analysis.     | HIGH         | ✓             | 1.5 | 4 |

Table 2.5.: Attack model: foundry.

| Asset  | Untrusted entity        | Example scenario(s)                                      | Threat level | Direct access | E   | I |

|--------|-------------------------|----------------------------------------------------------|--------------|---------------|-----|---|

| Layout | Infected third-party IP | Infected hard IP.                                        | HIGH         | ✓             | 1.5 | 4 |

| Layout | Employee(s)             | Manipulation of layout.                                  | HIGH         | ✓             | 1.5 | 4 |

| Chip   | Employee(s)             | Manipulation of dopant polarity of existing transistors. | HIGH         | ✓             | 2   | 4 |

Table 2.6.: Attack model: Assembly.

| Asset | Untrusted entity             | Example scenario(s)                                                  | Threat level | Direct access | E | I |

|-------|------------------------------|----------------------------------------------------------------------|--------------|---------------|---|---|

| Chip  | Infected third-party devices | Infected third-party devices.                                        | HIGH         | ✗             | 2 | 2 |

| Chip  | Employee(s)                  | Manipulation of the package by, e.g., appending antennas (triggers). | HIGH         | ✗             | 2 | 2 |

Table 2.7.: Attack model: OEM.

| Asset | Untrusted entity | Example scenario(s)                   | Threat level | Direct access | E   | I |

|-------|------------------|---------------------------------------|--------------|---------------|-----|---|

| Chip  | Employee(s)      | Exchanging devices for infected ones. | HIGH         | ✗             | 2.5 | 2 |

since the untrusted party has full and uncontrolled access to the asset. Note that the foundry sometimes includes an external mask house for mask generation. However, we assume that the mask generation is part of the fabrication process, thus being an untrusted environment.

## 2.2.6. Assembly

The assembly is considered an untrusted supply-chain stage. At this point in the chain, the hardware is already manufactured and placed in silicon. Thus, malicious changes on the design level are not possible. Nevertheless, the assembly facility can still manipulate and adjust the chip's packaging by, for example, adding malicious HW blocks or manipulating the packaging and pins. The attack vectors for this stage are listed in Table 2.6.

## 2.2.7. OEM

The OEM is considered an untrusted entity. In this stage, the design is already packaged. Thus, complex design changes are not possible. Nevertheless, the OEM can still exchange legitimate devices with infected ones. The attack vectors for this stage are listed in Table 2.7.

## 2.2.8. End Users

End users are considered untrusted. However, malicious manipulations are typically not an attack vector deployed at this stage of the supply chain. Nevertheless, end users can reverse engineer the chip, steal the IP, and extract secret keys.

### 2.2.9. The Cooperative Scenario

The attack models considered so far have been analyzed as individual stages with the assumption that no cooperation between multiple malicious entities exists—as typically assumed in the scientific community. However, it stands to reason that the inclusion of hardware Trojans is a complex and tedious process, especially if the HT should exert a high-impact and targeted attack. Therefore, a cooperative attack might be even more likely than just having a single, isolated malicious entity. One example of Trojan insertion could look like follows:

1. IP owner: An in-house malicious employee shares knowledge about what chip is being produced (e.g., processor) and for what purpose, i.e., the exact intended application domain (=control unit of an airplane).

2. External design house: The external design house inserts a design-dependent Trojan with the payload blocking the execution of instruction (=denial of service attack). The trigger is configured to listen to an external antenna.

3. Assembly: an external antenna is mounted within the package.

4. End user: a malicious employee (e.g., of an airplane construction company) inserts the infected processor into the target system (e.g., a specific airplane).

This attack scenario involves many untrusted parties across the supply chain. Thus, its implementation requires a high amount of planning, investment, and cooperation. However, its outcome might become more likely if untrusted parties are placed alongside the supply chain instead of having to design and insert a Trojan in a single step.

## 2.3. Threat Evaluation

The presented analysis in this chapter results in a clear message: the contemporary microelectronics supply chain is riddled with vulnerabilities. To provide more focus on high-priority vulnerabilities, we have introduced the effort and impact measures. Based on these measures, we can gather the following observations:

- A trusted environment can include low effort HT insertion, but typically results in low impact Trojans.

- An untrusted environment results in high-impact Trojans, specifically if direct access to the target design is provided. Thereby, it does not matter if the design and insertion of the Trojan is manual or automatic.

- All HT insertion scenarios in an untrusted foundry result in high-impact Trojans with a relatively low insertion and design effort.

- The lowest-effort and highest-impact HTs can be inserted by an external, untrusted design house operating on the RTL level.

The analysis confirms that external design houses and foundries pose the greatest threat within the microelectronics supply chain, and therefore, the primary focus of protection and detection research should be directed towards these supply-chain stages.

## 2.4. Open Challenges

- What effort, tools, and knowledge are required to insert a design-specific (class-1) hardware Trojan at different stages and abstraction levels in the supply chain?

- How to secure the hardware design while in the hands of external parties?

- How likely is a cooperative attack scenario, and how to protect against it?

# 3. The Untrusted Design House and Foundry

One of the most prevalent attack scenarios within the HW supply chain is the *malicious external design house and foundry* scenario. The reason that this scenario is frequently discussed within the scientific and industrial community is that most IP owners have to outsource parts of the design and fabrication services to third parties to uphold their business model. This reliance is driven by multiple factors, including tight time-to-market deadlines, lack of necessary skills, and exceptionally high construction and operational costs of semiconductor foundries [40; 41; 1]. As these third parties are often placed in off-site locations spread around the globe without any form of *assurance of trust* in the design and production process, a malicious modification, i.e., an HT, is a viable attack vector. Note that compared to other external entities, such as the assembly facility or the end user, both the external design house and the foundry receive the asset—the design files—in a form that is still "easily"<sup>1</sup> modifiable before it is hard coded into silicon.

In this chapter, we take a closer look at the conditions that enable an HT attack while the critical asset is in the hands of external parties. Section 3.1 summarizes the capabilities of the external parties. Section 3.2 introduced the concept of reverse engineering. Finally, Section 3.3 outlines the open challenges.

## 3.1. The Attack Model: Assumptions

The attack scenarios of an untrusted design house and foundry have been discussed in Section 2.2. The following is true for both malicious entities:

- The entity is considered untrusted.

- The entity receives full access to the design. The external design house receives either the RTL or gate-level design. The foundry receives the final layout.

- The entity operates without any restrictions or control by the legitimate IP owner.

- To insert a design-specific hardware Trojan (=class-1 Trojan as per Section 2.1.2.4), a certain amount of RE effort is required.

As we can see from the assumptions above, an important factor that determines the nature of the inserted Trojan is reverse engineering. Therefore, to understand the challenges and opportunities in Trojan detection and protection, we need to take a deeper look at the entire RE process.

---

<sup>1</sup> Compared to modifying the chip after the fabrication is done.

## 3.2. Reverse Engineering

Hardware RE is defined as the extraction of a set of specifications for a hardware design by someone other than the original design (IP) owner [42]. Thus, RE has historically been seen as a malicious act of significant relevance to governments, the military, and the industry. However, RE can also be utilized as a tool to check if the chip adheres to the intended specification, i.e., to exclude an infection with hardware Trojans or, simply, bugs. Evidently, in the context of malicious external entities, RE is used as a vehicle to decompose and understand the chip's functionality to insert a stealthy, design-specific hardware Trojan.

### 3.2.1. Flow

The primary objective of RE is to obtain an abstraction level of the asset that can be further analyzed and manipulated. In order to bring the asset to the most favorable abstraction level (ideally to its original specification), the attacker must invest a certain amount of Reverse Engineering Effort (REE). As the abstraction level of an asset decreases, a greater amount of REE is required to fully understand the design and insert C1HTs. The REE in each stage of the supply chain depends on various factors, including design complexity, level of obfuscation, availability of tools, human resources, financial resources, time, and others. Table 3.1 lists some of the available academic and industrial tools that only partially automate the RE process, which still requires manual pre- and post-processing steps. A fully automated, non-destructive, and zero-fault RE is not yet available. Furthermore, due to the sequential nature of the RE workflow, as illustrated in Figure 3.1, the correctness of reverse engineering an asset in one abstraction level depends on the accuracy of the RE process in the previous (lower) abstraction levels.

| Asset   | Untrusted entity                 | REE | Technology knowledge needed | Tools                                                                                                |

|---------|----------------------------------|-----|-----------------------------|------------------------------------------------------------------------------------------------------|

| Device  | End User OEM                     | 5   | Yes                         | Delayering and imaging tools [43; 44]<br>TAEUS, ScanCAD                                              |

| Chip    | Assembly                         | 4   | Yes                         | Delayering and imaging tools [43; 44]<br>ICWorks [45], ScanCAD, ChipJuice [46], TAEUS<br>Degate [47] |

| Layout  | Foundry<br>External design house | 3   | Yes                         | NETEX<br>ReGDS [48]                                                                                  |

| Netlist | External design house            | 2   | No                          | HAL [49], DANA [50]                                                                                  |

| RTL     | External design house            | 1   | No                          | VeriIntel2C, V2C                                                                                     |

Table 3.1.: RE tools: academic or industrial.

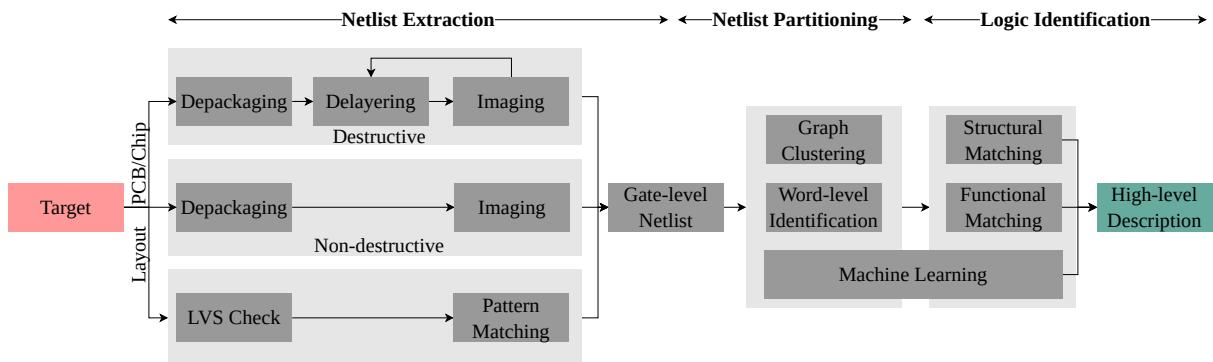

In the following sections, we will discuss different RE techniques performed by the untrusted entities in the supply chain, on different abstraction levels of the asset, starting from PCB/board level down to the netlist level. As shown in Figure 3.1, in the process of RE, the asset will change its format, however, this time in the opposite direction. A systematic study of the challenges for fully automated RE on different abstraction levels is presented in [51; 52; 53].

Figure 3.1.: Reverse engineering performed on different forms of the asset.

Figure 3.2.: An overview of the RE process on different abstraction layers of the asset.

### 3.2.1.1. PCB-level RE

The goal of PCB-level RE is to identify the components on the board (e.g., CPUs, memories, and communication ports) and their interconnections to determine the system's functionality and ultimately reconstruct the schematic of the board. This information can be used to clone the device or identify areas where potentially malicious features may be added. Integrated Circuit (IC) markings, manufacturer's logos, or die markings can easily identify some standard off-the-shelf components mounted on the PCB. In contrast, semi or fully customized circuits are typically not marked, and therefore more difficult to identify. Once the IC marking of a component is identified, the component's data sheet, if publicly available, can uncover detailed information about its functionality. After identifying the PCB components, it is necessary to determine the PCB type (e.g., single-sided, double-sided, or multi-layered).

PCB analysis can be destructive or non-destructive. A destructive RE process begins with PCB imaging to find the location and orientation of the components identified on the outer layers in order to remove them. The process continues with solder mask removal (i.e., desoldering) to expose the copper traces on the top and bottom layers. In a multi-layered PCB, the board is then delayered to access the inner copper layers. Images of each layer are taken to determine its composition (vias, connectors, and traces) and thickness [54]. Destructive PCB RE challenges and limitations are similar to those presented in Section 3.2.1.2, including accumulated errors and damage during desoldering and delayering (e.g., broken traces and disconnected vias), low-quality images, and others. Non-destructive PCB-level RE is performed using X-ray computed tomography (X-ray CT) which eliminates the delayering process and speeds up the PCB imaging time [55]. By using X-rays, a radiograph of the object is produced, which shows its composition, thickness, and any defects that may be present. An object's internal structure is visualized without the interference of overlayer and underlayer structures. The images captured during destructive delayering or non-destructive X-ray imaging are analyzed, and a PCB layout netlist is constructed. The layout could ultimately be converted into board schematics using commercially available software. Although impressive, the results depend heavily on the construction features of the PCB. In addition to high machine costs, the non-destructive method is further limited by the field of view of the X-ray system, which can make it difficult to obtain high-quality X-ray images of the entire PCB area [54; 56; 57]. Tear Apart Everything Under the Sun (TAEUS) is a service provider that offers PCB and chip-level RE to discover infringements within a product. ScanCAD is another service provider that uses destructive and non-destructive methods for PCB RE to generate schematics of the board.

During the manufacturing process, PCBs can be subjected to malicious modifications. A malicious

---

modification is usually detected by comparing the reconstructed PCB schematic with a golden PCB schematic, which is an image taken from a PCB manufactured by a trusted and authorized source. However, since this report focuses on malicious modifications at the IC level, we will not examine further attacks and countermeasures on the PCB level [58; 59; 60].

### 3.2.1.2. Chip-level RE

The goal of chip-level RE is to identify the internals of the chip and ultimately retrieve its functionality at a higher level of abstraction. Chip-level RE consists of two phases, physical RE and functional RE, as illustrated in Figure 3.2. Physical RE extracts the gate-level netlist from the physical chip, while the subsequent functional RE understands its functionality and specification. This section takes a closer look at the techniques for physical RE. Functional RE is described in the following sections.

As with PCB-level RE, chip-level RE can also be destructive and non-destructive. A typical chip consists of a die, a lead frame, wire bonding or solder bumps, and a molding encapsulant. Chips are packaged with ceramic or plastic materials, using wire bond or flip chip packaging techniques. Destructive RE of a packaged chip involves several steps [45; 57]. The chip is first depackaged (or decapsulated) to recover the die using chemical, mechanical, laser ablation, or Focused Ion Beam (FIB) methods. The die is then cleaned to prevent dust-related artifacts from affecting any subsequent stages. Methods which achieve high material removal accuracy and affect a specific controlled area (e.g., plasma FIB, laser ablation) are expensive and require a high level of operational skills. To acquire images of all chip layers, delayering and imaging are performed alternately. The number of layers, their material and thickness, vias, and connectors are identified by cross-sectional imaging using Scanning Electron Microscopy (SEM), Transmission Electron Microscopy (TEM), FIB, or Helium Ion Microscopy (HIM). Due to its wide availability and reasonable cost, SEM is the most commonly used tool for IC imaging. The delayering process is then performed in multiple stages, usually by combining wet/plasma etching, grinding, and polishing [61; 62]. Due to variation in chip thickness caused by manufacturing process variations, it is best to have one die for each delayering stage. Mechanical equipment used for chip delayering includes: semi-automated polishing and milling machine, CNC milling machine, ion beam milling machine, laser, and others. To recreate the chip, a number of high-resolution images of each layer are taken, stitched together, and analyzed to recover the circuit [63; 61]. The circuit analysis includes automated and manual steps. An automated image recognition software is used to identify the cells from the standard cell library and obtain the transistor-level netlist. Extraction of gates by defining the functionality of the identified standard cells is a non-automated process, usually as a result of the unavailability of standard cell libraries. To detect stitching errors and imperfections caused by the image recognition process, design rule checks are performed [45]. After the entire area is processed, the gate-level netlist is obtained. These steps are followed by a functional interpretation of the results, as described in Section 3.2.1.4.

Although destructive techniques for chip-level RE are still the most prevalent, non-destructive approaches also exist. Non-destructive chip-level RE is performed using X-ray computed tomography (X-ray CT) which eliminates the delayering process and speeds up the PCB imaging time for the upper metal layers of an IC. X-ray CT can resolve features in ICs up to 14.6 nm in size [64]. However, it is associated with significant overhead in the image acquisition time frame. This method is not yet perfect, and it does not provide as much information about the chip's internals as invasive techniques. Future developments may make it a significant non-destructive RE tool. Photon emission microscopy can also help in RE by probing and decoding IC functionality in

---

near-infrared spectra, but cannot be exploited for full-scale RE. Scan chain RE, on the other hand, is a non-destructive RE method that exploits the scan chains inserted into the device for production test to allow easy access to the circuit internals. This technique gives a netlist approximation that is logically equivalent to the netlist [65].

The process of destructive chip-level RE is complex, expensive, time-consuming, and only partially automated. Each step in the process requires a high level of precision and operational skills. Images might be imperfect, cell image recognition could be erroneous, and consequently stitching for nanoscale node technologies becomes challenging. Therefore, a certain error rate is expected in the final netlist. In practice, the error rate should be less than 1%. Generally, technology libraries are proprietary, which could be a problem for RE performed by OEMs and end users.

There is limited support from industry and academia for chip-level RE. Degate [47] is an open-source framework for reverse engineering ICs. The tool generates a gate-level netlist after receiving layer images and a standard cell library, but it does not offer support for further netlist analyses. There are several commercial service providers that offer tools for chip-level RE. ChipWorks (now merged with TechInsights) developed ICWorks [45], which provides destructive techniques for netlist extraction and subsequent analysis. Texplain developed ChipJuice [46], an automatic RE tool which can process layer images and, if given the standard cell library, reconstructs the netlist.

### 3.2.1.3. Layout RE

External design houses and foundries with access to the GDSII layout files of the design can perform a layout RE without the need to go through the tedious and expensive RE steps described in the sections above.

ReGDS [48] is a layout RE framework that reconstructs the transistor-level netlist based on the GDSII layout files and the technology library, and after identifying the logic gates, recovers the original gate-level netlist. The framework first uses Layout vs Schematic comparison (LVS) tools to extract the transistor-level information, and subsequently uses graph matching algorithms to facilitate logic gate identification.

### 3.2.1.4. Netlist RE

As mentioned in Section 3.2.1.2, chip-level RE consists of two phases, physical RE and functional RE. While physical RE extracts the netlist from a given chip, the goal of functional (netlist) RE is to obtain a high-level description of the chip's functionality for further interpretation and validation. The approaches described in this section assume that the gate-level netlist is previously extracted using the mechanisms described in Sections 3.2.1.2 and 3.2.1.3. A systematic description of the methods and algorithms for netlist RE is given in [53].

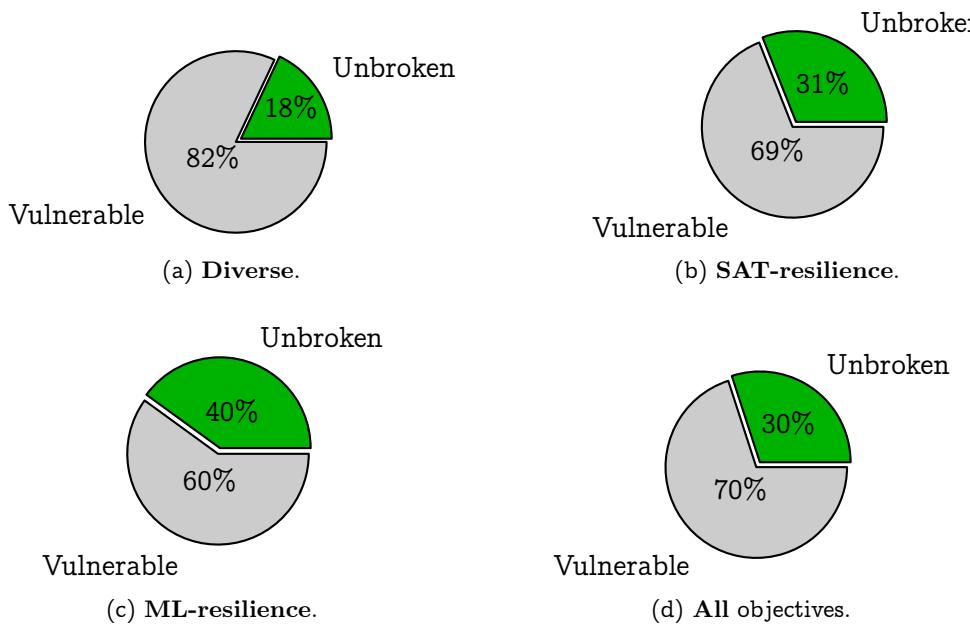

The netlist RE itself consists of two phases, netlist partitioning and logic identification (Figure 3.2). Netlist partitioning is performed on the flattened netlist, which does not contain any information regarding the hierarchy, boundaries, and functionality of modules. The netlist is broken down into smaller structures (i.e., submodules), which are then analyzed separately. Several approaches for netlist partitioning exist, including word-level structure identification [66; 67; 68] and graph clustering [69; 70; 71; 72].