cyberagentur

# ECOSYSTEM FOR TRUSTWORTHY IT LOS 3: FORMAL VERIFICATION OF HARDWARE-SOFTWARE- INTERFACES

Christoph Lüth,

Dieter Hutter,

Milan Funck,

Jan Zielasko

Version 1.0 (Final Version) | 31st January 2023

Herausgeberin:

Agentur für Innovation in der Cybersicherheit GmbH

## **Disclaimer**

Die hier geäußerten Ansichten und Meinungen sind ausschließlich diejenigen der Autorinnen und Autoren und entsprechen nicht notwendigerweise denjenigen der Agentur für Innovation in der Cybersicherheit GmbH oder der Bundesregierung.

Diese Studie wurde durch die Agentur für Innovation in der Cybersicherheit GmbH beauftragt und finanziert. Eine Einflussnahme der Agentur für Innovation in der Cybersicherheit GmbH auf die Ergebnisse fand nicht statt.

## **Impressum**

Herausgeberin: Agentur für Innovation in der Cybersicherheit GmbH

Große Steinstraße 19, 06108 Halle (Saale), Germany

E-Mail: [kontakt@cyberagentur.de](mailto:kontakt@cyberagentur.de)

Internet: [www.cyberagentur.de](http://www.cyberagentur.de)

Twitter: <https://twitter.com/CybAgBund>

Die Nutzungsrechte liegen bei der Herausgeberin.

Lizenz: CC BY-NC-ND 4.0: <https://creativecommons.org/licenses/by-nc-nd/4.0/>

Erscheinungsdatum: 12.07.2023

Redaktion: Abteilung Sichere Systeme, Referat Sichere Hardware und Lieferketten

# **Ecosystem for Trustworthy IT (Ökosystem vertrauenswürdige IT)**

## **Lot 3: Formal Verification of Hardware-Software-Interfaces**

---

Christoph Lüth, Dieter Hutter, Milan Funck, Jan Zielasko

Version: 1.0 (Final Version)

31st January 2023

### **Abstract**

We report on the state of the art in the area of formal verification at the hardware-software interface. Following a systematic survey of the literature covering the last ten years, we can give a landscape of existing verified systems and verification tools. Verification methods have come of age, with verified operating system kernels, compilers, and hardware, but there are still substantial gaps, in particular with respect to security; we detail these research needs and propose directions for future research efforts.

# Contents

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                              | <b>2</b>  |

| <b>2</b> | <b>Formal Verification</b>                                       | <b>3</b>  |

| 2.1      | Safety and Correctness . . . . .                                 | 3         |

| 2.2      | Security . . . . .                                               | 3         |

| 2.3      | Structuring Mechanisms . . . . .                                 | 4         |

| 2.4      | Challenges of the Hardware-Software-Interface . . . . .          | 5         |

| 2.5      | Verification Methods and Tools . . . . .                         | 6         |

| 2.6      | Summary . . . . .                                                | 9         |

| <b>3</b> | <b>State of the Art</b>                                          | <b>9</b>  |

| 3.1      | Formalization and Verification of ISAs . . . . .                 | 9         |

| 3.2      | Memory Models . . . . .                                          | 12        |

| 3.3      | Programming Languages . . . . .                                  | 13        |

| 3.4      | Verification of System Software . . . . .                        | 15        |

| 3.5      | Verification of Systems . . . . .                                | 16        |

| 3.6      | Security . . . . .                                               | 16        |

| 3.7      | Capability Hardware Enhanced RISC Instructions (CHERI) . . . . . | 17        |

| 3.8      | Summary . . . . .                                                | 20        |

| <b>4</b> | <b>Research Needs and Roadmap</b>                                | <b>20</b> |

| 4.1      | Research Needs . . . . .                                         | 20        |

| 4.2      | Roadmap . . . . .                                                | 22        |

| 4.2.1    | Small Projects . . . . .                                         | 23        |

| 4.2.2    | Technology Research & Development . . . . .                      | 24        |

| 4.2.3    | Foundational Research . . . . .                                  | 25        |

| 4.2.4    | Dependencies and Priorities . . . . .                            | 27        |

| 4.3      | Summary . . . . .                                                | 28        |

| <b>A</b> | <b>Literature Survey Statistics</b>                              | <b>51</b> |

# 1 Introduction

For a system to be *trustworthy*, it is a necessary precondition that the complete system is correct, from the applications running on the system down to the hardware. Correctness, as understood here, means that there is a formal specification of the intended behaviour of the system, to which the system adheres.

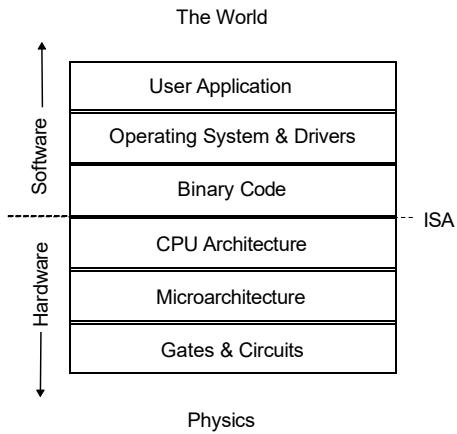

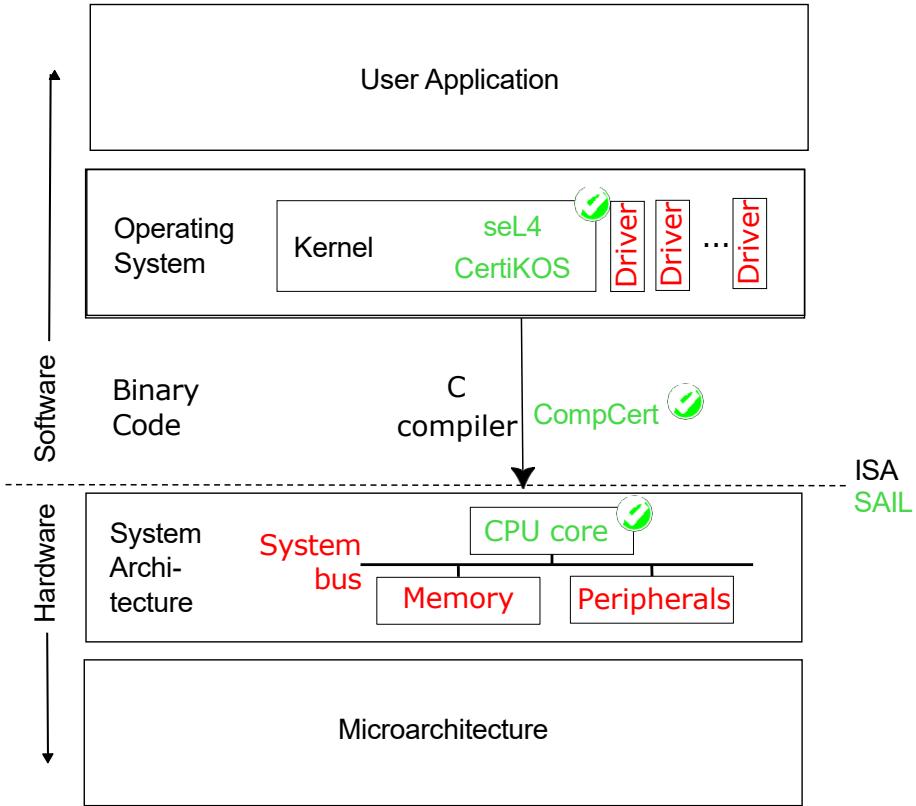

This comprehensive notion of correctness (the “whole stack” or end-to-end) requires interfaces and abstractions between the different layers of the system. Figure 1 shows the typical layers of abstraction in a system (inspired by [85]): a system is grounded in the physics underlying its electronics. From simple gates and circuits, a CPU is built with a specific microarchitecture. The most prominent abstraction layer is between the hardware and the software. This interface is defined by the *instruction set architecture* (ISA) of the hardware, which defines how the hardware behaves as seen by the software. In the software, we abstract more and more from the concrete implementation, first by an operating system which hosts user applications (including possibly more layers such a hypervisor between the hardware and the operating system), second by a virtual machine on which applications run. They form the interface of the system to the outside world, the latter being either the human user or an environment in which the system acts, or a network of other machines.

Structuring the system in such a way raises the question how correctness, which is usually stated at the user-visible upper levels (the “world”), can be transferred and proven at the lower levels. This question is exacerbated by the vastly different languages and development paradigms in hardware and software. This makes formal verification at the hardware-software interface challenging.

The *scope* of this report lies on the challenges we face when formally verifying the correctness of combinations of hardware and software. We are concerned with formal proofs, rather than exhaustive testing or hardware-in-the-loop tests, and our focus is on the layers in Figure 1 which are not greyed out; in other words, the correctness of low-level system software (operating system, device drivers, hypervisors) and the ISA, but not correctness of the microarchitecture, nor correctness of software applications, which are covered by other lots. However, the question how to cross the boundary between hardware and software and verify correctness properties of a complete system is also relevant here.

The structure of this report is as follows: Section 2 revisits the basics of formal verification, with a focus on specific challenges of verification at the hardware-software interface. Section 3 presents the results of a systematic survey of the state of the art, where we have surveyed and evaluated the publications of the last ten years in relevant conferences. Finally, Section 4 details

Figure 1: Layers of abstraction.

future research needs, and proposes a roadmap for future efforts.

## 2 Formal Verification

Trustworthy systems have to be safe against threats from the outside (attacks) and from the inside (defects). The former is broadly subsumed as security, the latter as safety.

### 2.1 Safety and Correctness

Typical safety properties state the system satisfies a given specification. The specification can pertain to the required functional behaviour of the system, *i.e.* specifying which response is expected to which input, or the non-functional behaviour, which specifies response time, power consumption, memory consumption (for software) or die area (for hardware); consequently, we speak of *functional* and *non-functional correctness*. Functional correctness can be stated in terms of conditions on the input, or starting state of the system, implying conditions on the output, or end state of the system; these can be formulated in a variety of logics (see below), and take the form of contracts or assume-guarantee pairs. Going beyond these simple mechanisms, we can formulate requirements in formal modal logics such as LTL or CTL [134]. Non-functional properties are formulated either directly (“System must always respond within 20  $\mu$ s.”), or by extending specification mechanisms with the required dimension (*e.g.* timed automata, duration calculus, hybrid automata [5, 40, 88]). Typically, violations of such safety conditions can be eventually detected by monitoring the behaviour (*e.g.* run-time checks) of a system [4]. This will change if we consider security requirements.

### 2.2 Security

An important class of non-functional properties are *security properties*. Classical security properties like confidentiality or integrity are typically enforced by access control, or information flow control mechanisms. Ultimately, an access-control policy regulates for each pair of subject (process) and object (data) which actions are allowed to be executed. Access control policies are represented in a structured way, for instance, by means of roles [62] or capabilities [57] to ease their formalization and maintenance. While access control policies regulate the access to data, they do not consider the information stored in the data. In contrast, information flow control policies regulate the flow of information between different subjects (or security domains) within a program. Hence, instead of controlling the access to confidential data, information flow control regulates the effect of confidential information to the (visible) behaviour of a system. *E.g.*, whenever running a program twice with same public input (but different secret ones), the visible behaviour of both runs are indistinguishable. Data hidden to an observer must not affect the (part of the) behaviour of the system seen by the observer. As a result, the violation of such requirement can only be detected by comparing different runs of a system. In theory,

they represent closure properties on sets of possible system runs (called hyperproperties) [45], which are out of range for a run-time monitor to check.

In an operating system, for instance, a kernel has to isolate different processes from each other to ensure that actions of one process can only influence other processes in an authorized way. However on a hardware level, resources, like memory or I/O-devices, are typically shared between various processes. Uncontrolled access of processes to shared resources would enable unauthorized information flow between them using the common resource as a covert channel (Information filed into the resource by one process is read by the other process). Hence, access to resources are usually implemented via a virtualization of (physical) resources hiding their real physical addresses and therefore preventing that a process can circumvent the access control. Furthermore, virtualization must hide any dynamic property of a resource that is influenced by the behaviour of other processes from the process (providing temporal/spacial separation). Typical examples are the response time when accessing memory (caching!) or the occupancy of a device by other processes. Since communication between processes requires the ability of at least one process to change the stored information in the resource, shared access to static information like physical locations of devices do not constitute a covert channel.

## 2.3 Structuring Mechanisms

To build large systems, we need to be able to structure both the development and the properties of the system into smaller constituent pieces, and introduce well-defined interfaces between them. For these structuring operations, we distinguish between:

- *Horizontal structuring* decomposes a complex system into smaller components, and includes modularization into components, aggregation of similar components, composition and decomposition.

- *Vertical structuring* links models on different abstraction levels by refinement (or abstraction in the inverse direction).

For verification, the interesting question is whether structuring operations preserve the property in question, *i.e.* whether we can prove properties of the whole system by proving properties of the constituent parts, and combine them. This is called *compositionality*. In general, safety properties are compositional, but security properties are not (although the specifics depend on the particular properties: functional correctness of sequential programs is compositional, but neither non-functional correctness nor correctness of concurrent programs).

The idea of *refinement* is to construct a model of the system at a higher level of abstraction, where we can show the required properties, and then derive a system model at a lower level where the properties are preserved. This technique is used quite often in verification, often implicitly. For example, the verification of the seL4 kernel is conducted with respect to an abstract model written in a functional language; this can be seen as a refinement from an abstract model in a high-level language down to a concrete model in an efficient low-level language [113].

There are two ways to work with refinements: one can either construct two models, and show *post facto* that the concrete model refines the abstract one, or one can construct the concrete model from the abstract one step-wise, by applying refinement operations which are guaranteed to preserve correctness [15]. Related to this is the idea of *cross-level verification* [82, 35], where different abstraction levels are used simultaneously to achieve greater coverage, by relating properties stated at the abstract level to the implementation provided on a lower level.

As mentioned above, refinement allows one to translate valid (safety) properties about an abstract system to concrete properties about its implementation by applying a series of correctness-preserving transformations. In contrast to the safety case, security properties specified and proven in an abstract system do not uniformly translate to valid properties about a realized system. Roughly speaking, security properties relate the abilities of an (unknown) adversary to successfully attack the system. Each refinement will provide the adversary with a new (refined) vocabulary, which they can arbitrarily use to formulate an attack, while any attack mentioned on the abstract level will be refined, *i.e.* implemented to a particular attack in the refined layer.

## 2.4 Challenges of the Hardware-Software-Interface

Verification on the hardware-software-interface can be challenging, because it combines two very different computational paradigms, worlds views and resulting development flows.

Hardware is costly to produce, and immutable. This means that errors are very costly to fix (for example, Intel’s infamous Pentium FDIV bug resulted in a cost of 475 million dollar<sup>1</sup>). Subsequently, hardware development is very engineering-driven, with an emphasis on correctness at the cost of flexibility; errors are not tolerated. Software, on the other hand, is flexible, can be produced at hardly any cost once developed, and can be changed reasonably easily afterwards. This results in a more agile development methodology, which puts an emphasis on flexibility and change; errors are tolerated, and corrected once detected.

Hardware has a smaller state space compared to software (*e.g.* a fixed set of registers as opposed to a large number of variables), making it more amenable to automatic proof methods such as model checking and symbolic execution via SMT-provers. Software has a larger state space, and also a larger vertical development space—the abstraction levels range from the ISA over low-level software (device drivers, operating system) to user applications. The hardware of a system is typically described in one language (a hardware description language, HDL, such as VHDL or Verilog), whereas a number of languages are used for the software—from the binary machine code described by the ISA over low-level languages such as C to higher-level languages such as Java or Javascript (ECMAScript) to domain-specific languages describing particular application areas, reflecting the vertical design space described above.

One problem when combining different formalisms is that we have to guarantee *consistency*, in the sense that shared symbols are given the same meaning, and that no contradictions are generated. This is typically achieved by embedding the formalisms into a more general one

<sup>1</sup>Source: Intel Corporation 1994 Annual Report, via Wikipedia.

(specification languages like UML, first-order or higher-order logic, type theory *etc.*), or by a well-defined interface linking both sides (the prime example of this being the ISA).

Beyond that, when combining hardware and software we have to consider the properties of the system *as a whole*, which combines both worlds multiple times. For example, a typical application has a software stack (user-interfacing application code running on a Java virtual machine, running in an operating system which serves as an interface to the hardware), and properties are formulated at the abstract level (*e.g.* a credit card number entered in the application must remain private), but have to be proven across multiple abstraction layers (here, from application code down to micro-processor executing binary machine code, and the keyboard-driver actually recording the number as it is entered). Fortunately, the ISA is a well-defined interface between hardware and software, but it may need to be extended for the case at hand (*e.g.* when considering peripherals such as the keyboard). Thus, we need a methodology how to transfer properties between hardware and software — from the software world to the hardware and back. This discussion links with the compositionality from previous Section 2.3; here, linking software applications to hardware is a vertical structuring operation, and we are interested which properties are preserved.

In general, as mentioned before, safety properties (defined as properties of each run of the system) are preserved from the software to the hardware, but security properties (defined, for instance, as a closure property on the set of possible system runs) are not. Precisely because hardware is so radically different from software, a whole new Pandora box of threats opens up. New covert channels are available on the hardware level, based on execution time, power consumption, race conditions, or even caching behaviour inside CPU-cores that potentially disclose evidence of code execution to a hostile observer and thus open new avenues for side-channel attacks. Software compartments being the main aids in security to separate individual activities must be mapped in terms of temporal or spatial separability on a hardware level giving rise to the need to thoroughly monitor and control provenance and flow of information on all channels even partially observable by an adversary.

## 2.5 Verification Methods and Tools

Verification methods and tools need to handle these challenges. In general, the question whether a given system satisfies a given property is undecidable; it becomes decidable once we limit ourselves to systems with a finite state space. Then, verification needs to consider all possible system runs (or states) to check that the required properties are satisfied. However, the number of states (the state space) becomes too huge as to make the question practically undecidable for realistic systems. There are three principal tools which help us to handle this problem: The first is *compositionality*, which allows us to decompose the state space of the overall system into the smaller state spaces of its components; the second is *abstraction*, which allows us to reduce the state space while preserving the properties to be shown; and the third one is *automated theorem proving*, which shows a property not by state enumeration but by logic inference rules.

Unfortunately, state abstraction is very much dependent on the particular property; it can be

used as abstract interpretation to great effect in *e.g.* showing that no exceptions or no integer overflows occur [139]. Model checking is a general term for a family of techniques where the system is modelled as a finite state machine, with a smaller state space than the original one, properties are formulated in variations of temporal logic (LTL, CTL, timed logics) and proven by state exploration. This technique can be efficient for safety properties, and useful because it can provide concrete counter-examples, but in general awkward to show absence of faults.

Theorem proving can be divided into automated theorem proving, where the logical inference rules are applied without user guidance, and interactive theorem proving, where the human user guides the rule application. Automated theorem proving works well with decidable fragments of certain logics, *e.g.* Presburger arithmetic with linear inequalities as used in SMT provers (or solvers) such as Z3. These provers are very powerful in their niche, but often used invisibly as verification engines behind the scene in verification tools; there is even a standard interface language SMTlib to allow interchangeability between these tools.

Modern interactive provers such as Isabelle or Coq make use of automated provers by using them to prove trivial lemmas which are then combined into more comprehensive results. Isabelle has a sophisticated methodology for this (called Sledgehammer [27]), which uses automated provers to explore the state space, and reconstructs the proof inside Isabelle, without compromising the provers' consistency. Table 1 shows an overview, without any claim of completeness, over the existing proving tools, as used in the state of the art as surveyed in Section 3.

Symbolic execution is state exploration combined with theorem proving, by expressing the state evolution as a logical formula. Originally developed for software [110] modern tools such as KLEE [36] can be very efficient when considering moderate to large state spaces. Related to this is the technique of predicate abstraction, where predicates over integers are reduced to equivalent predicates over boolean variables [18, 44, 65].

In the context of verification in the hardware-software interface, the methodology of *virtual prototyping* [55, 129, 90] is relevant as well. A virtual prototype is an implementation of the hardware in software, in particular of the microprocessor but comprising the whole system including peripherals as well, and using a high-level systems modelling language such as SystemC or SpinalHDL. Originally developed for early software development to enable software development before hardware is physically available, virtual prototypes can be used for verification purposes as well, *e.g.* by using symbolic execution to show correct behaviour [34, 194].

| Name                                 | URL, Details                                                                                                                                                                                              |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interactive provers                  |                                                                                                                                                                                                           |

| Isabelle/HOL <sup>a</sup>            | <a href="https://isabelle.in.tum.de/">https://isabelle.in.tum.de/</a><br>Typed higher-order logic with automated prover support and tactics, rich user interface, large library of available theories.    |

| Coq                                  | <a href="https://coq.inria.fr/">https://coq.inria.fr/</a><br>Inductive calculus of constructions, dependent types, rich library of available theories. Recipient of the 2013 ACM Software System Award    |

| K                                    | <a href="https://kframework.org/">https://kframework.org/</a><br>Rewrite-based semantic framework for the definition of formal operational semantics                                                      |

| ACL2                                 | <a href="https://www.cs.utexas.edu/users/moore/acl2/">https://www.cs.utexas.edu/users/moore/acl2/</a><br>Inductive first-order logic with term rewriting. Recipient of the 2005 ACM System Software Award |

| HOL4                                 | <a href="https://hol-theorem-prover.org/">https://hol-theorem-prover.org/</a><br>Typed higher-order logic. Slightly dated but still in widespread use.                                                    |

| Alloy                                | <a href="http://alloytools.org/">http://alloytools.org/</a><br>Relational logic (as in UML). Fully automatic, with integrated model finder.                                                               |

| Maude                                | <a href="http://maude.cs.illinois.edu">http://maude.cs.illinois.edu</a><br>Rewriting logic engine                                                                                                         |

| Dafny                                | <a href="https://dafny.org/">https://dafny.org/</a><br>Programming language with integrated specification language and program verifier                                                                   |

| Automatic provers and model checkers |                                                                                                                                                                                                           |

| Z3                                   | <a href="https://github.com/Z3Prover/z3">https://github.com/Z3Prover/z3</a> , SMT prover                                                                                                                  |

| Alt-Ergo                             | <a href="https://alt-ergo.ocamlpro.com/">https://alt-ergo.ocamlpro.com/</a> , SMT prover                                                                                                                  |

| Yices                                | <a href="https://yices.csl.sri.com/">https://yices.csl.sri.com/</a> , SMT prover                                                                                                                          |

| Spin                                 | <a href="https://spinroot.com">https://spinroot.com</a><br>Model checker, Recipient of the 2002 ACM System Software Award.                                                                                |

| nuSMV                                | <a href="https://nusmv.fbk.eu/">https://nusmv.fbk.eu/</a><br>Model checker for synchronous and infinite-state systems                                                                                     |

<sup>a</sup>Isabelle is a generic theorem prover, and Isabelle/HOL the specific instance of Isabelle for classical typed higher-order logic; this is the only Isabelle logic ever used in this field, so here when we refer to Isabelle, we mean Isabelle/HOL.

Table 1: Overview of theorem proving tools used in verification.

## 2.6 Summary

- We distinguish safety and security properties. The former include functional and non-functional correctness, and can be decided in terms of input and output of a single run; the latter include confidentiality, privacy, and integrity, and are not decidable on a single system run.

- Horizontal structuring operations construct the system from smaller components, and vertical structuring operations relate models of the system at different levels of abstraction (refinement). Compositional properties are preserved by horizontal structuring; safety properties are compositional, whereas security properties are not.

- Verification at the hardware-software interface is a challenge because of the different computational paradigms and world views (languages, tools, development flows). This makes it hard to transfer properties, in particular security properties, from software to hardware or vice versa. The central interface of the system is the interface from the hardware to the software, the instruction set architecture (ISA).

## 3 State of the Art

To systematically survey and assess the existing literature, we have reviewed all papers in the last ten years from leading conferences (and journals) in the field of formal verification, looking for papers in the area of hardware-software verification. Specifically, we were interested in

- formalization and verification of ISAs,

- verification and development of low-level software (as defined above),

- and tool support for these activities.

The specifics and statistics about our approach can be found in Appendix A.

### 3.1 Formalization and Verification of ISAs

*Formalization* of an ISA means the construction of a model in a format which can be read and processed by a computer. We have found 12 papers concerned with this endeavour. The languages used for this purpose can be diverse; they range from programming languages or HDLs such as Haskell or System Verilog to theorem provers such as the K framework, ACL2, Isabelle, or Coq, to domain-specific languages (DSLs) invented for this specific purpose, such as SAIL and its precursors. Most industrially relevant ISAs have been formalized, including ARMv8,

| Name, Refs         | ISA     | Language       | Notes                                                                        |

|--------------------|---------|----------------|------------------------------------------------------------------------------|

| [178]              | x86     | HOL4           | Model of x86-TSO in HOL4                                                     |

| [140, 53]          | x86     | K              | Fully executable semantics, uncovered bugs in manual                         |

| RockSalt [143]     | x86     | Coq            | Checking software-based fault isolation                                      |

| CORANA [197]       | ARM     | Z3             | Extracts formal semantics from natural language spec. for symbolic execution |

| [75]               | x86     | ACL2           | Verification of x86 machine code                                             |

| [69]               | ARMv7   | HOL4           | Formalizes ARMv7 ISA                                                         |

| [166]              | ARMv8   | DSL            | Describes formal language ARM uses to specify ARMv8 architecture             |

| GRIFT [176]        | RISC-V  | Haskell        | Sequential simulation, coverage analysis                                     |

| riscv-formal [204] | RISC-V  | System Verilog | Formal testbenches for RISC-V cores                                          |

| [182]              | RISC-V  | Kami           | Used by SiFive                                                               |

| SAIL [9]           | Generic | DSL            | Not tied to specific ISA, used for ARMv8, RISC-V, MIPS                       |

Table 2: Overview of recent ISA formalization efforts.

x86, MIPS, and RISC-V. The formalization efforts are summarized in Table 2. One point to note is that the x86 ISA proved so complex that there has been work to learn its behaviour from running programs [91, 195].

The first objective of the formalization efforts was to obtain an unambiguous and precise description of the behaviour of the hardware, which the software running on the machine can rely on. This was then used as a basis for verification (see next section), but also to check consistency of the specification [207], to check conformance of hardware designs to the ISA [204], to model the micro-architecture [67], to verify machine code running on that architecture [75, 143, 135] or compilers targeting it [106].

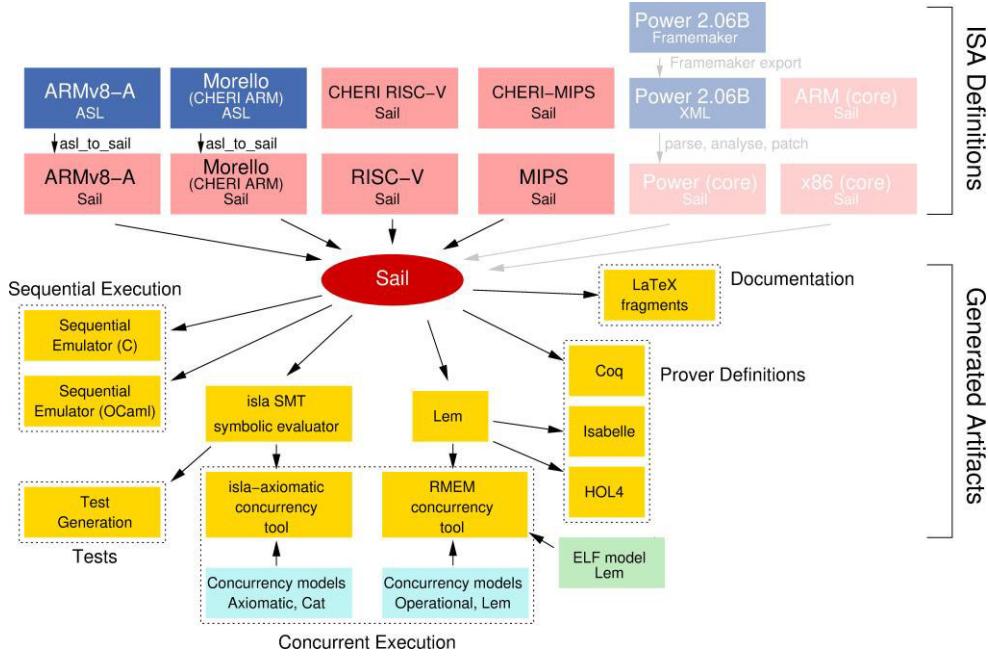

A prominent recent development is SAIL, a domain-specific language used to specify instruction set architectures. Its precursors can be found, *inter alia*, in the language used by ARM to specify their ARMv8 architecture [68, 166], but it has since then been used to specify the ARMv8 architecture, MIPS, and RISC-V; for the latter, it has been adopted as the ‘gold standard’ by RISC-V international. The value of SAIL is that ISA specifications are completely unambiguous, readable for engineers, and can be used to generate code for theorem provers or other analysis tools. Figure 2 gives an overview of the SAIL architecture and tool landscape. From the generic description of an ISA, the SAIL tools can generate sequential emulators. Moreover, the Isla tool [11] proves symbolic execution for SAIL ISA specs, which is used in [11] to generate tests from a specification (taking the weak memory semantics into account). The Islaris tool [174] uses the symbolic execution engine together with the Iris formalization of separation logic in Coq to verify ARMv8 and RISC-V machine code. Via translation to the Lem language [146], a prover-independent higher-order language to model semantics, defini-

| Name, Refs       | ISA      | Language                            | Notes                                                           |

|------------------|----------|-------------------------------------|-----------------------------------------------------------------|

| ISA-Formal [167] | ARMv8    | DSL, Verilog                        | Industrially used at ARM                                        |

| Forte [105, 152] | x86 (i7) | DSL <sup>a</sup>                    | Industrially used at Intel                                      |

| [72]             | RISC-V   | Cadence Jasper,<br>BlueSpec Verilog | Verification focuses on CHERI extensions to ISA                 |

| [93]             | SPARCv8  | Isabelle                            | Proves non-interference for LEON3                               |

| [75, 54, 76]     | x86      | ACL2                                | Industrial verification of an embedded x86 processor at Centaur |

| Bedrock [61]     | RISC-V   | Kami                                | Simple core, part of stack covering whole embedded system       |

| CSLED [208]      | x86-32   | Coq                                 | Derives consistent instruction encoder/decoder                  |

<sup>a</sup>Combines own theorem prover with model checking (symbolic trajectory evaluation).

Table 3: Overview of recent ISA verification efforts.

tions of the ISA in Coq, Isabelle and HOL4 can be obtained. (Circumstantial evidence suggests that these generated models are not easy to work with.) SAIL has furthermore been used to specify the CHERI architecture, an experimental extension of standards ISAs with so-called *capabilities* (see Section 3.7).

*Verification* of an ISA means ensuring that an implementation of the ISA in hardware (the micro-architecture) behaves as formally specified. As opposed to software, in hardware formal verification — meaning *proving* that the micro-architecture behaves as *formally* specified — is more established. Table 3 gives an overview about recent ISA verification efforts, as they appear in the literature; note entries by Intel [105] or ARM [167] using formal verification as part of their design flow. It is further stated [72] that “formal verification methodologies for [RISC-V instructions] are well-established”, so it is safe to assume that formal verification in industrial practice is well established and not always published (an observation corroborated by personal experience), and hence more wide-spread than Table 3 suggests. Still, there are two main problems: firstly, verification which is not published may be of use to the manufacturer but not to the user — in particular, a formal model of the ISA to be verified against must be available, such that users can base software verification on it. This is not always the case, *e.g.* for the x86 ISA. Secondly, most of the papers and efforts are concerned with functional correctness of the ISA; this is sufficient for safety properties, but verification of security properties may require properties beyond what the ISA can express ([12] is a step in this direction).

A substantial body of work is concerned with languages to model hardware; just like the programming languages for software, hardware description languages (HDL) are evolving constantly. Recent HDLs in this direction include Kami [42], which is integrated into the Coq theorem prover, and allows seamless correctness proofs; Chisel [14] and SpinalHDL [153] (the latter a fork of the former) which evolved from the RISC-V community at Berkeley, and Clash [13], which are built on functional languages with all the advantages that come with them;

Figure 2: Overview of the SAIL architecture and tool landscape.

or more recent languages such as PDL [210] targeted at pipelined processors.

### 3.2 Memory Models

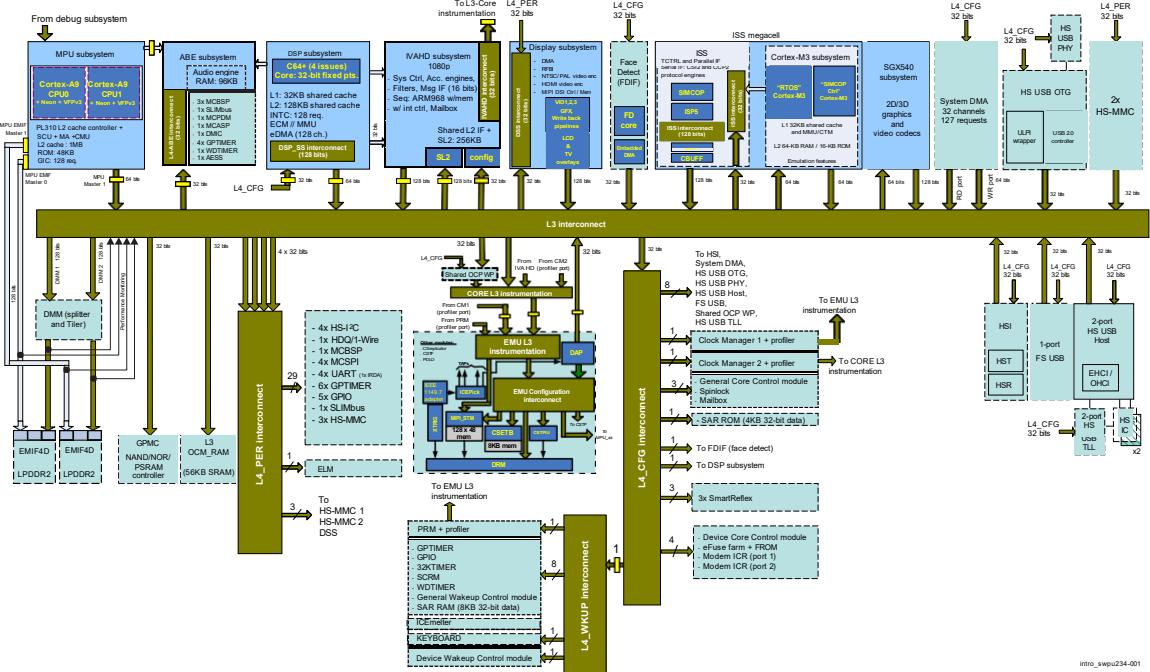

A surprising amount of work concerns memory models, *i.e.* the behaviour of memory as observed from the software. This is partly because memory access is typically either not part of the ISA, or only in a very simplified fashion. The typical assumption [2] is “a per-core virtual address space translated, at page granularity via a memory management unit (MMU), to a single global physical address space containing all the random access memory (RAM) and memory mapped devices in the system.” However, in typical modern SoCs the situation is far more complex; Figure 3 shows the block diagram of the (at time of writing slightly dated) TI SoC OMAP 4460 (quoted in [2]); as we can see, addresses can be remapped in a multitude of ways, even creating loops if configured incorrectly. The paper [2] presents an embedding of configuration models for a memory bus into Isabelle, and allows *e.g.* consistency proofs to exclude such pathological situations; other work [190, 191] addresses the question how such complex memory models impinge on the formal verification of programs using them.

This situation is mirrored on the software side by the memory model of programming languages, in particular C. The C standard views memory as “objects, composed of contiguous sequences of one or more bytes.”[50, Section 6.2.6.1 (2)], and does not even assume one contiguous address space. All modern compilers and operating systems assume a more detailed model here, making use of “implementation-defined behaviour” as permitted but not described by the standard. This means that verifications are always specific to a particular configuration of machine architecture and compiler used. A number of papers [138, 127, 142] propose

**Figure 1-2. OMAP4460 Block Diagram**

Figure 3: Block diagram of the TI OMAP 4460.

©Texas Instruments, Source <https://www.ti.com/lit/ug/swpu235ab/swpu235ab.pdf>

extensions which allow the portable verification of realistic programs (such as OS kernels).

Other papers address the problem of concurrency in the presence of weak memory models. Modern processors rarely access the memory in precisely the sequence as given by the program, creating additional problems (for example, the recent Spectre/Meltdown bugs were caused by speculative execution, where memory was accessed before the program reached the corresponding instructions). One way out of this problem is by total store ordering (TSO); [163, 109] formalize this for x86 architectures. [162] presents an approach allowing to explore other such models formally, and [48, 132] propose DSLs to build memory models complete with reasoning support, [60] even with a purpose-built model checker, and [96] with a focus on hardware extensions. Languages and provers used here include Isabelle, Alloy, Maude, and Dafny.

However, in summary it is fair to say that finding memory models which are both abstract enough to allow efficient verification of software utilising the memory and at the same time precise enough to capture the hardware behaviour accurately enough remain an active research area.

### 3.3 Programming Languages

For all its faults [117, 138], C is the dominating language when writing low-level software. C is portable, well-known, and has excellent and diverse tool support. This is reflected in the literature: in our survey, we have found 13 papers concerned explicitly with the C language

(not counting those verifying software written in C), three with assembly language, two with Rust, and one each with Scala, Lustre, and Esterel. As far as the foundations go, the established consensus is the use of some variant of Hoare logic, extended with separation logic to handle references and pointers.

Apart from papers discussing deficiencies of the language, in particular the standard<sup>2</sup>, and suggesting remedies [138, 175, 127], the main bulk of this work was concerned with verified compilation. A milestone in this area was the first verified C compiler CompCert [128] by Leroy and others, who have been awarded the 2021 ACM System Award for this achievement. Subsequent work and papers have built on this, for example:

- The Verified Software Toolchain [6, 7] by Appel and others uses CompCert to build a tool chain which guarantees correctness from the source down to the machine-language program running on a weakly-consistent-shared-memory machine, much in the spirit of Sir Tony Hoare’s verifying compiler [92].

- Various papers are concerned with extensions to CompCert to include separate compilation [188, 107], linking [164], or inclusion of assembly language [186] (as is common in low-level code).

- A fork of CompCert is used as the compiler for the verified operating system kernel CertiKOS [80, 81].

- Other extensions cover “stack awareness”, *i.e.* ensuring programs do not run out of stack space [198, 38].

A different approach is to define a DSL (*e.g.* RESOLVE [165, 192] or CIVL [86]) which is expressive enough to cover interesting programs without the entrenched difficulties of a long-established language, but compared to work on C this seems to have been rarely followed up.

Apart from C, the language Rust has recently gained a lot of traction [101], but there is not much work (yet) on large verification efforts using Rust, even though the RustBelt project [100, 51] has laid the necessary foundations for this. An interesting recent development is to extend C with ownership types (RefinedC, [175]), combining established tool support for C with one of the main innovations of Rust.

Furthermore, there is work on verifiable assembly languages [30, 70, 21, 151], which make use of the comparatively simple structure of assembly language to automate proofs, but this seems a rather niche application (*e.g.* Vale [30, 70] is used in the context of cryptography). Notably, we did not find many references using Ada or SPARK [19] apart from [71], even though it is an established framework to develop high-quality software, suggesting its use is in the aerospace domain rather than system software. Similarly, Esterel [66] and Lustre [32] are used in the context of real-time systems, and Scala [121] is not a systems programming language.<sup>3</sup>

<sup>2</sup>There is some overlap here with the work on memory models discussed in Section 3.2, as these are a part of the standard, and hence the language, and in fact one of its main deficiencies.

<sup>3</sup>For the same reason, the substantial body of work concerning verification of the Java platform, including the

### 3.4 Verification of System Software

Early work on the verification of operating systems dates back to the eighties (see [112, Table 2] for an overview), but these did not concern realistic kernels. Recent efforts include seL4 and CertiKOS; Table 4 also shows a number of industrial entries, demonstrating that formal software verification has arrived in the main stream. This also means, as discussed above, that there may be industrial verification projects which have not been published, *e.g.* it is unclear whether Microsoft actively maintains the proofs for the Hyper-V hypervisor, and there are rumours about verification activities at Apple. On the other hand, the start-up Prove& Run has announced a verified kernel [28, 29] but not published any details or papers about this work.

The two verified OS kernels, CertiKOS and seL4, exhibit the two main contemporary approaches to kernel development. CertiKOS<sup>4</sup> is the *Certified Kit Operating System*. It is not a micro-kernel, but a full kernel with scheduler, file system, and various hardware drivers. It uses an intricate layer-based framework to guarantee correctness of the whole kernel, where specifications (and components) can be layered on top of each other. Components can be written in C or assembler; a fork of the CompCert compiler covers correctness of the linking process as well, and guarantees correctness of the whole kernel. All proofs are done in the Coq theorem prover. In contrast, seL4<sup>5</sup> is a microkernel, derived from the L4 family of microkernels. It formally proves the isolation of applications running on the system in Isabelle/HOL. There is an ecosystem of tools surrounding seL4, *e.g.* the CAmkES and sDDF framework which allow driver development for seL4 [155], but these are not part of the formal correctness proof of seL4.

The verification of device drivers started in earnest with the use of predicate abstraction [18, 17]. Predicate abstraction is a technique to reduce the state space of a program to make them amenable to model-checking, while preserving the validity of the properties in question, such as program safety, memory leaks or conformance to an API protocol. Tools like C2BP [18] (part of the SLAM suite) or BLAST [181] implement the technique, and are used for static driver verification in Windows [16] and Linux [161] respectively, although the latter seems not actively maintained any more. There has been work on formalising network protocols (TCP, [169]) or file systems ([170]); more recent efforts include mCertiKOS [41] or Vigor [157].

One prominent tool suite for the verification of C programs is Frama-C [111] (even though it was not used in any of the papers we have surveyed). In Frama-C, specifications are added as specially formatted comments (annotations) in the E-ACSL language. It combines various static analysis techniques with the verification condition generator Why3 [63] to prove these assertions. It is actively maintained and used in various industrial projects [23].

---

programming language and the JVM, has been omitted from this survey, as Java is not a systems programming language. It might be interesting to consider a verified JVM as a virtualization layer, allowing user applications only on this virtual machine (as in the Android OS); there is work such as [83] (which we did not explore) in this direction.

<sup>4</sup><http://flint.cs.yale.edu/certikos/framework.html>

<sup>5</sup><https://sel4.systems>

| Name and Refs   | Prover        | Notes                                                                                                                              |

|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| VeriSoft [47]   | Isabelle, VCC | Used VCC to show separation property of Microsoft Hyper-V hypervisor; not actively maintained any more                             |

| seL4 [113, 179] | Isabelle      | Proves functional correctness and security properties                                                                              |

| CertiKOS c[81]  | Coq           | Certified abstraction layers for correctness and safety                                                                            |

| SyberX [207]    | Isabelle      | CC evaluation to EAL5+                                                                                                             |

| NOVA [24]       | Coq           | Proves confinement properties for NOVA hypervisor                                                                                  |

| OSEK [56]       | nuSMV         | Proves correct configuration of customised kernels                                                                                 |

| N.N. [39]       | Iris, Coq     | Proves correctness of IPC algorithms for new microkernel at Meta                                                                   |

| VERVE [209]     | Coq, Boogie   | Verifies correctness at the binary level by compiling to typed assembly language and showing refinement from abstract model in Coq |

Table 4: Kernel verification efforts.

### 3.5 Verification of Systems

A substantial body of work is concerned with the verification and validation of complete embedded systems; application highlights include the control software for the Chinese lunar rover [180], and an ERTMS Railway train spacing system [43]. If industrial standard languages are used for verification, they need to be given a formal semantics, *e.g.* AADL<sup>6</sup> [126, 125] or the UML [168]. However, most of these efforts focus on the software, constructing a model of the software which can be verified [89, 160, 64, 3]. Another approach to verified control software is to generate code, often using control theory [154, 89, 122]; this is lacking a hardware angle and so is not considered further in this report. Another left-field area is verification of CUDA kernels [145, 58]; although this is low-level according to our definition, we consider CUDA not to be essential components of trustworthy systems.

When verifying complete systems, we need to consider consistency across the hardware-software border, *i.e.* when verifying the correctness of the ISA against its specification, and verifying the correctness of the software running on that ISA, we need to be sure that both specifications of the ISA are at least consistent. Not a lot of work has been concerned with that aspect; in [61] a verification of this kind is carried out for a simple embedded system, embedding all the specifications inside one common framework (*viz* the Coq prover). It seems debatable whether this approach scales to larger systems (with an operating system, multiple drivers, and user applications running on it).

### 3.6 Security

The previous verification efforts are mostly concerned with functional correctness or program safety properties. Covering security we review a few papers investigating protection against

<sup>6</sup>Architecture Analysis & Design Language, an SAE standard for the avionics industry

| Name and Refs      | Prover        | Notes                                                                                                      |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------|

| Microsoft SDV [16] | SLAM          | Uses predicate abstraction and static analysis to verify safety of Windows device drivers                  |

| Linux SDV [161]    | BLAST         | SDV for the Linux eco-system                                                                               |

| mCertiKOS [41]     | Coq           | CertiKOS covering device drivers and interrupts.                                                           |

| SybilFS [170]      | Lem           | Provides a model of POSIX file system, derives test oracles                                                |

| [169]              | HOL4          | Provides high- and low-level models of TCP and sockets API, proves correctness, provides validation tests. |

| PerSeVerE [118]    | model-checker | Formalizes semantics of ext4 file system, can model-check programs to use its API correctly.               |

| [157]              | Vigor         | Formal verification of a NAT stack.                                                                        |

Table 5: Driver verification efforts

side-channel attacks before detailing the CHERI approach.

The Scam-V tool [147] allows validating observational models (using symbolic execution) against real hardware, to detect side channels by generated test programs. [59] uses SMT solvers for a similar objective, showing data is perfectly masked. In contrast, [185] formally shows (using Isabelle) threat security (absence of data leaks) for weak memory models, in particular for ARM architectures. [49] develops a general methodology (in Coq) for the mCertiKOS verified operating system for security proofs, using a general notion of observation for *e.g.* state indistinguishability; this approach covers the whole software stack, but does not cover the underlying hardware. [87] describes an approach to prevent timing channel attacks, both on the hardware and software side. This has been implemented and evaluated for seL4 [73] for the x86 and ARM processors, and for RISC-V [203] leveraging additional hardware support. It is currently being verified [184].

SAFE [12] is a “clean-slate design for highly secure computer systems”, comprising both hardware and software, with formal end-to-end proofs of non-interference. The hardware considered in SAFE is assumed to have capabilities beyond what one would usually expect from an ISA, much in the spirit of CHERI.

### 3.7 Capability Hardware Enhanced RISC Instructions (CHERI)

The CHERI approach [205, 202] extends standard ISAs with architectural capabilities that allow for a fine-grained access control of memory on a HW-level. These capabilities are unforgeable tokens of authority supporting a highly scalable software compartmentalization as well as the realization of a secure (*i.e.* monitored) software (C or C++) pointers.

In principle, capabilities relate to portions of the address space and define the permissions that owners of the capabilities possess on them. They can be marked as invalid (withdrawing

the associated permissions) or as sealed (disabling any modifications and usage). Capabilities are protected by the architecture of the ISA. They can only be constructed by instructions that do so explicitly and new capabilities cannot exceed the permissions or address space of the capabilities underlying its creation. In particular, this gives rise to a security property of capability monotonicity on code execution. The set of capabilities accessible to the code cannot increase during its execution (preventing privilege escalations) unless execution is yielded to another domain.

While at boot time the firmware is equipped with initial capabilities covering the entire address space, in each stage of the software stack (boot loader, hypervisor, operating system, processes, etc.) address space and permissions of the related capabilities will become more restrictive in accordance to the monotonicity property. Another property is the intentionality of credentials, such that if a process passes a capability as an argument to a system call, the kernel can use only that credential to guarantee that no other process memory covered by other capabilities of the kernel is accessed. To deal with capabilities, CHERI introduces special and general capability registers and adds new ISA instructions operating exclusively on capabilities in these registers (ensuring intentionality!).

CHERI also supports the use of C/C++ language and virtual-memory-based software by a hybrid capability architecture to integrate a capability model with a conventional MMU-based architecture. In particular, it constrains integer-related memory access by a default data capability and instruction fetches by a program-counter capability.

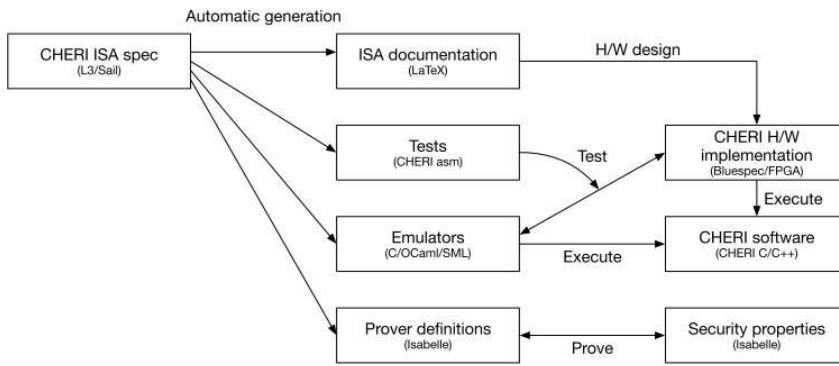

CHERI extensions to 64-bit MIPS and 32/64-bit RISC-V ISA are specified in the SAIL-language (*cf.* Section 3.1) and are available as open source<sup>7</sup>. These SAIL specifications are the starting points to derive reference documentations, ISA-level simulators in C or OCaml, hardware instruction tests as well as emulators and prover definitions of the architecture for a formal verification in Isabelle/HOL, COQ or HOL4 (*cf.* Figure 4).

Figure 4: Main artefacts of the CHERI engineering process as in [202].

The CHERI extensions have been formally verified using the Isabelle prover with respect

<sup>7</sup>CHERI-MIPS: <https://github.com/CTSRD-CHERI/sail-cheri-mips>,

CHERI-RISCV: <https://github.com/CTSRD-CHERI/sail-cheri-riscv>

to the various security properties [149]. These are in particular, 1. that they satisfy the monotonicity and intentionality properties, 2. that arbitrary code cannot change system registers or memory without having explicit permissions to do so, and 3. guarantees about the execution of untrusted code in a controlled isolation boundary.

There are two main use cases of CHERI capabilities with respect to C/C++ based software stacks concerning fine-grained memory protection and scalable software compartmentalization.

**Fine-grained memory protection.** The use of capabilities instead of integers to implement C/C++-language pointers, and minor extensions to operating system and language runtime-system enable a strong and efficient spatial, referential, and temporal memory safety for these traditionally memory-unsafe languages. CHERI allows for two compilation modes. In a pure-capability mode, in particular all pointer types (of C/C++) are realized by capabilities. Then, the architecture preserves the integrity and the provenance of the pointers, thus preventing an injection of pointer values from outside or an in-memory corruption of pointers. Narrowing the bounds of the address space and restricting permission (typically done by the compiler) prevent pointers from being abused for purposes other than for what they were intended.

**Scalable software compartmentalization.** Following the MILS-paradigm [173], conventional MMU-based software compartmentalization decomposes larger software applications into components running in isolation and communicating only in a controlled way. Capabilities open up an alternative means to construct the software isolation and controlled communication required to implement compartmentalized software designs. Unlike MMU-based compartmentalization (*i.e.*, implemented using virtual memory), capability-based techniques allow for more granular and scalable data sharing, as they are restricted by page-granularity sharing and the utilization of multiple address spaces and thus the number of compartments.

CHERI comes with an adapted reference stack for its architecture realizing the benefits of capabilities. This includes extended versions of the real-time operating system FreeRTOS and the BSD-based operating system FreeBSD as well as its own CheriOS microkernel demonstrating in particular granular compartmentalization together with strong memory safety. Common developer tools like Clang/LLVM compiler, LLD linker and GDB debugger are extended to support the CHERI architecture. Finally, various extended user-space libraries and applications are also available.

### 3.8 Summary

The state of the art can be summarized as follows:

- Established instruction set architectures are the x86 and ARM families, and more recently RISC-V. For all of these, formalizations and verification support are available. The SAIL language and framework allow convenient tool development for all ISAs.

- C is the *lingua franca* of system development, and has been investigated thoroughly. There is a verified C compiler, CompCert, and a number of verification tools such as Frama-C, or specialized theories for Isabelle or Coq.

- There are at least two verified operating systems, seL4 and CertiKOS, which have left the prototype stage and are actively supported.

The state of the art covers all layers of interest in Figure 1. We consider all tools to be at least at TRL 5 as defined in the Horizon 2020 work programme<sup>8</sup>. However, there are still open questions which need to be addressed. This will be the subject of the final section.

## 4 Research Needs and Roadmap

### 4.1 Research Needs

In Figure 5, we have mapped the results of our survey in the last section to the system layers in Figure 1. Note that the major points for a trustworthy system in the hardware-software region are covered — there are verified operating system kernels, a verified compiler for the most widely used language, C, and three major instruction set architectures which have been formalized and verified (marked in green in Figure 5). However, we can also see that there are necessary parts of a system which are not verified (these are marked in red). The most relevant gaps here include:

- *hardware drivers*: CertiKOS integrates drivers into the kernel and has support for the verification of the driver and the whole kernel; it remains to show this scales well in practice. seL4 handles drivers outside the trusted kernel, relying on the kernel for correctness.

- *memory buses*: there is a lot of work on memory buses, but it needs to be extended to cover complex memory protocols and configurations as found in complex SoCs and systems.

- *peripheral devices*: there is scant work on handling connection to peripheral devices, *e.g.* hard disks, but we cannot simply disregard these.

<sup>8</sup>[http://ec.europa.eu/research/participants/data/ref/h2020/wp/2014\\_2015/annexes/h2020-wp1415-annex-g-trl\\_en.pdf](http://ec.europa.eu/research/participants/data/ref/h2020/wp/2014_2015/annexes/h2020-wp1415-annex-g-trl_en.pdf)

Figure 5: Trustworth systems and tooling landscape.

Moreover, the verified parts are as yet not coupled together in a comprehensive manner, nor is there a systematic way how the verification can connect to verified parts in the hardware (microarchitecture), or user applications. For the microarchitecture, while we know how to specify the ISA and verify its functional correctness, the connection of the SAIL language to hardware description languages, in particular innovative new ones like Chisel or SpinalHDL, needs improvement. The connection to user applications needs more work: essentially, it needs a comprehensive specification of what an operating system does. Of course, seL4 and CertiKOS have formal specifications, but it is unclear (and unlikely) if they are sufficient. The situation gets even more interesting when we consider security aspects, such as confidentiality, privacy or compartmentalization. Proving such properties formally will require more comprehensive specifications, and specification formalisms covering the whole system stack, possibly even across the software-hardware border; the CHERI extension built on SAIL (*cf.* Section 3.7) is a good starting point in that direction.

A further question to consider is *licensing*. Most of the tools and components mentioned above are available under open-source licenses. We posit that open-source licenses are crucial for a trustworthy environment, as they allow users and developers to analyse and scrutinize the source code to assess its correctness. In theory, it might be sufficient to provide a formal specification of the interface along with a formalized proof of correctness, but this has not been shown to work with substantial developments or security properties. On the hardware side,

|                                    |                      |

|------------------------------------|----------------------|

| Verified OS kernel                 | seL4, CertiKOS       |

| Verified C compiler                | CompCert             |

| ISA specification and verification | SAIL                 |

| Verified CPU cores                 | diverse RISC-V cores |

| Provers                            | Isabelle, Coq        |

Table 6: Suggested best-of-breed tools and system components.

proprietary IP such as ARM cores might be of more use, given that they are delivered in source form, and thus at least susceptible to automatic analysis techniques.

Finally, one needs to consider *long-term viability* of both the components and the development tools. The x86 ISA is by now dated and very complex, as a result of maintaining backwards compatibility for forty years; its long-term prospects are unclear.<sup>9</sup> The long-term prospects of ARM and RISC-V look much better (even if the latter is still lacking widespread industry acceptance). As for languages, the C language has been with us for fifty years, and will probably stay with us for another fifty. It is supported by several excellent compilers, including CompCert. Other languages such as Rust which might take up the mantle as premier system programming language are still young and one-compiler languages. This is a problem in the long run; for long-term viability we need diversity on the supply side, being able to choose among different compilers, or in the case of hardware, OEMs.<sup>10</sup> This lack of diversity may be a problem for the long-term viability of verification proofs as well. Both Coq and Isabelle are built using a specific compiler (Coq uses OCaml, Isabelle uses Poly/ML), with which they interact quite closely; and both provers, although open-source, are maintained by a small group of academic volunteers. None of this discussion means tools and languages such as Rust, Isabelle or Coq should not be considered, but one should be aware of these issues, and investigate possible alternatives. This in particular means to provide well-defined interfaces between components, specified in a language which is not dependent on any one tool. (SAIL is a good example of this; a framework like Frama-C and its specification language E-ACSL could be the basis for a similar rôle for software verification.)

To sum up, for the hardware-software interface we have a number of languages and tools at our disposal; Table 6 gives an overview of the best-of-breed which can serve as a basis to build an ecosystem of trustworthy systems.

## 4.2 Roadmap

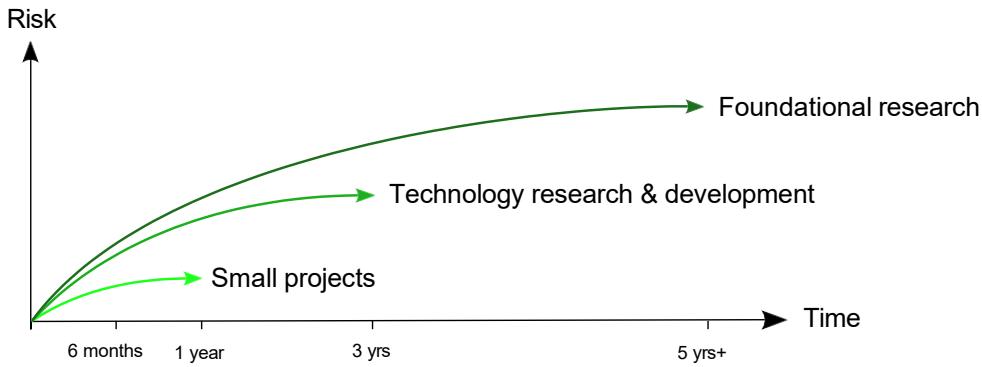

Based on the discussion in the previous section, we will lay out a roadmap of research projects focussed on the hardware-software interface. We classify projects according to their *risk* and

<sup>9</sup>In particular given Intel's recent announcement of a billion-dollar investment in RISC-V <https://www.electronicdesign.com/technologies/embedded-revolution/article/21216435/electronic-design-intel-launches-1-billion-fund-to-build-foundry-ecosystem-backs-risc>.

<sup>10</sup>This makes ARM viable in the long term, because there are a lot of hardware suppliers for ARM-based hardware.

Figure 6: Classification of research projects.

the *time* horizon in three categories (Figure 6):

- (i) *Small projects* have a clear technological focus, which fill gaps in the tool and component landscape. They do not require major new research or large developments. These are low-risk (it is highly likely they will succeed in the stated goal), and require something like 6 to 12 person months.

- (ii) *Technology research & development* are medium-sized projects where new technologies, algorithms or tools need to be developed. They are of medium risk (they may fail, but with appropriate risk management some of the research efforts should always be recovered), and take times between 36 and 72 person months (typically, three years with one to three persons). These are the typical BMBF-funded projects.

- (iii) *Foundational research* is research where at the start not much more than basic research questions are known, and the project develops foundations, methodologies and tools to solve the question. Comparable to DFG-funded projects, these are of high risk (they are as likely to fail as to succeed, but they should fail productively, providing a negative answer to the research question) and last anytime between 24 and 50 person months.

#### 4.2.1 Small Projects

These are small projects with a well-defined scope, using existing technologies and methods. Following are a few suggestions:

- (S-1) *Extend SAIL with support for functional HDLs* like SpinalHDL, Chisel or Clash. Presently, SAIL can generate tests as System Verilog Assertions, but if one wants to verify conformance of a SpinalHDL design, one needs to manually translate the SAIL specification to SpinalHDL.

- (S-2) *Connect SAIL to riscv-formal and Symbiyosys*. This would integrate SAIL, and the 'gold standard' RISC-V specification in SAIL, to the existing RISC-V tool.

(S-3) *Provably correct RISC-V ISA specifications.* The RISC-V specification generated from the SAIL specification in Isabelle via Lem is not very readable or friendly to work with. In order to be able to better work with it, we can define a more succinct spec directly in Isabelle and formally show equivalence with the generated specification.

(S-4) *Rebase the seL4 verification to SAIL.* The current seL4 verification is based on the ISA modelled in Isabelle/HOL. It needs to be investigated whether it is easier to replace this ISA model with the specification of the RISC-V ISA specification from the previous project, or whether one proves equivalence of this specification and the official RISC-V ISA separately.

(S-5) *Connect SAIL to existing virtual prototypes.* There exist a number of virtual prototypes, in particular for RISC-V systems, but most of them are based on independent formalizations of the RISC-V standard; connecting them with the existing SAIL standard would give increased confidence.

(S-6) *Virtual prototyping support for CHERI.* In a similar vein, adding support for the CHERI extensions to existing virtual prototypes for RISC-V would open the way to develop software making use of these extensions before RISC-V hardware supporting CHERI is available.

(S-7) *Connect CompCert with SAIL.* The CompCert compiler has its own model of the binary code produced at the end; connecting this to existing SAIL standards would close a gap and contribute to an idea of overall correctness.

(S-8) *Extend SAIL with support for Rust.* Currently, SAIL supports C and OCaml, but support for Rust in the same form as with C would help with developing system software in Rust.

There may be more, similar projects here that will come up during the more long-term projects sketched in the following. It makes sense here to set up a framework where these projects can be applied for and granted in an agile, light-weight way, as for example with Google’s Summer of Code projects. These would also serve as good student projects. As students are an import avenue of dissemination, we recommend setting aside funding for this specific purpose.

#### 4.2.2 Technology Research & Development

Other gaps in the tool landscape require a more comprehensive effort. These are the main gaps that we have identified:

(R-1) *Comprehensive verification of a realistic embedded system, e.g. a router.* This would show how the tools work together, and identify further gaps in the landscape; it would also indicate how to structure a fully verified system, and how to connect the tools. As opposed to [61], this system would preferably not be implemented in one single theorem prover, but connect the different provers and formalisms from the tool landscape.

(R-2) *Safe and secure peripherals.* Components such as network stacks or file systems are essential to any operating system. There has been early work in this direction [169, 170]. A fully verified implementation of a network stack and POSIX-compliant file system is a substantial effort, and still lacking.

(R-3) *Drivers and peripherals for seL4.* There is already work on how to implement drivers for seL4, and how to extend seL4 to a full operating system ([155], *cf.* discussion above on page 15), but this has to the best of our knowledge this has not been subject to formal verification (as opposed to CertiKOS [41]). After setting up a methodology to add drivers, integration of the results of the previous project would seriously enhance seL4’s verified capabilities.

(R-4) *Extend Frama-C with ownership types and capabilities.* There is research in extending C with ownership types, bringing the benefits of Rust into the C world. In this project, it should be investigated how Frama-C, and in particular its specification language can be extended to that effect; the ownership types would be the software equivalent of the hardware capabilities on the CHERI side. The project would require

- defining a suitable annotation syntax and semantics;

- adding support to Frama-C to check these annotations;

- or adding support to the prover tools (the Jessie plug-in, which is currently not actively maintained).

When successful, this would extend Frama-C as a development and verification interface for CHERI-based code.

(R-5) *A formally verified virtual prototype.* Virtual prototyping has proven a valuable tool in early software development, *i.e.* developing software for hardware which is under development. However, none of these have been formally verified to the extent that *e.g.* CompCert has. Such a formally verified VP would be a valuable addition to the ecosystem.

(R-6) *A formally verified Rust microkernel.* In order to diversify the ecosystem in terms of language support, develop a fully verified microkernel in the Rust language. This is a good test for the tool support of Rust, in particular the verification support (the Rustbelt tool) and if the fragment of Rust covered by verification support is large enough. Of particular interest would be how to integrate external modules into the kernel, as Rust can distinguish between safe and unsafe code; it would be favourable if driver code could always be safe.

#### 4.2.3 Foundational Research

Beyond filling gaps, there are some issues that require a more foundational approach.

(X-1) *Comprehensive security.* Much of the discussion and projects in the previous section, as much of the previous work on formal verification from Section 3, is concerned with functional, and to a lesser extent, non-functional correctness. The software tool stack (as well as its underlying basis in hardware) is aligned to efficiently support the realization of a given functionality but provides only few means (if any at all) to explicitly constrain an (automated) refinement process by demanding non-functional or security requirements. An example would be to demand that information stored in particular variables must not influence the generation of communication messages. In this situation, a compiler should adjust the intended memory allocation of variables within a program according to the formulated security needs and in line with the security measures provided by the hardware. CHERI is a good start in this direction, and can serve as an anchor to develop a tool stack which provides means for formally verified security. The main task would be to lift the guarantees provided by the hardware via the ISA into security notions on higher level (user applications). This includes the development of a vocabulary of security notions on the programming level and of compiling techniques to refine these notions into sufficient requirements on an ISA-level. Subsequent steps include investigating if CHERI is powerful enough to support these aspects, or needs extending. There is also the aspect of extending the verification tools in the landscape to handle CHERI. The end vision here is a system with formally verified secure enclaves.

(X-2) *Reference architecture for trustworthy systems.* In the long run, the actual components of a safe and secure, fully verified computing landscape are not as important as the interfaces between them. Single components will always become out of date over time, and may need to be replaced, but the basic interfaces will remain stable. This concerns

- the hardware-software interface (the ISA),

- the memory bus and other busses connecting peripheral devices to the CPU,

- the interface of the kernel to the various driver modules,

- the interfaces of major operating systems (such as file systems and network stacks), and

- the interface of the operating system kernel to the user applications.

It extends beyond the components to the tools. A reference architecture should specify specification and modelling languages, independent of the tools (provers) used.<sup>11</sup>

The reference model should include comprehensive tests, and where possible automatic prover tools, for all components, in particular for drivers, as in the Microsoft SDV. This is particularly relevant, as drivers are a frequent source of erroneous behaviour (in particular, system crashes).

---

<sup>11</sup>One will probably need to fix the programming language for practical reasons, but should strive for multi-language support.

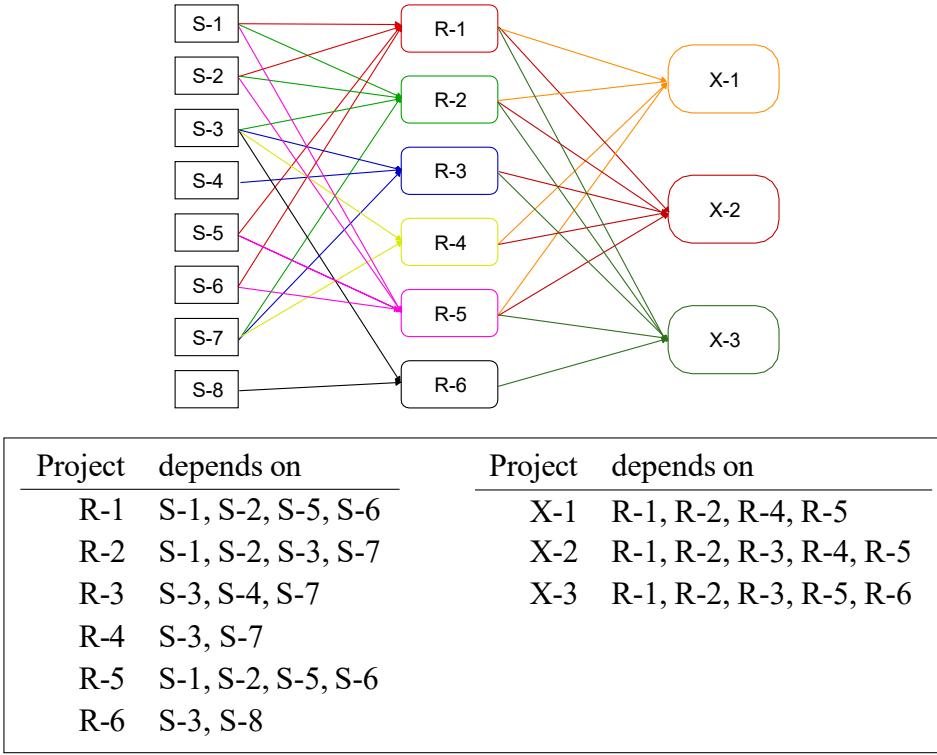

Table 7: Dependencies between proposed research projects.

(X-3) *Proof engineering*: how to structure and conduct huge formal proofs. A formally verified ecosystem of trustworthy systems relies on formal proofs, but there is not much work as yet on the construction of such proofs. Early pioneering efforts such as the proofs of the Four Colour theorem, the Kepler conjecture or the Feit-Thompson theorem have been heroic efforts by sole individuals rather than concerted group efforts, as opposed to the situation in hardware or software development, where *e.g.* the Linux operating system has seen countless contributors over the years.