# **ECOSYSTEM FOR TRUSTWORTHY IT**

## **LOS 2:**

# **FORMAL SECURITY**

# **VERIFICATION OF**

# **HARDWARE**

Wolfgang Kunz,

Dominik Stoffel,

Johannes Müller,

Mohammad R. Fadiheh

Fachbereich Elektrotechnik und Informationstechnik, Rheinland-Pfälzische Technische Universität

Version 1.0

Herausgeberin:

Agentur für Innovation in der Cybersicherheit GmbH

## **Disclaimer**

Die hier geäußerten Ansichten und Meinungen sind ausschließlich diejenigen der Autorinnen und Autoren und entsprechen nicht notwendigerweise denjenigen der Agentur für Innovation in der Cybersicherheit GmbH oder der Bundesregierung.

Diese Studie wurde durch die Agentur für Innovation in der Cybersicherheit GmbH beauftragt und finanziert. Eine Einflussnahme der Agentur für Innovation in der Cybersicherheit GmbH auf die Ergebnisse fand nicht statt.

## **Impressum**

Herausgeberin: Agentur für Innovation in der Cybersicherheit GmbH

Große Steinstraße 19, 06108 Halle (Saale), Germany

E-Mail: [kontakt@cyberagentur.de](mailto:kontakt@cyberagentur.de)

Internet: [www.cyberagentur.de](http://www.cyberagentur.de)

Twitter: <https://twitter.com/CybAgBund>

Die Nutzungsrechte liegen bei der Herausgeberin.

Lizenz: CC BY-NC-ND 4.0: <https://creativecommons.org/licenses/by-nc-nd/4.0/>

Erscheinungsdatum: 12.07.2023

Redaktion: Abteilung Sichere Systeme, Referat Sichere Hardware und Lieferketten

# LOT 2 – Formal Security Verification of Hardware

*Wolfgang Kunz, Dominik Stoffel, Johannes Müller, Mohammad R. Fadiheh*

Fachbereich Elektrotechnik und Informationstechnik, Rheinland-Pfälzische Technische Universität

Version 1.0

This study provides an overview on methods of formal hardware verification in view of relevant security objectives for the *basic IT elements* in hardware at the microarchitectural level. We derive the targets of sign-off security verification from an analysis of common hardware weaknesses and the relevant security requirements for microarchitectures. The study relates these targets to the state of the art in formal hardware verification and describes strengths and weaknesses of different methods and methodologies. This leads to research recommendations for formal security verification of hardware.

## Table of Contents

|            |                                                                                     |    |

|------------|-------------------------------------------------------------------------------------|----|

| 1.         | Introduction – Microarchitectural Security of Hardware.....                         | 3  |

| 2.         | Security Goals – Microarchitectural Security Risks and Verification Objectives..... | 3  |

| 2.1.       | Security Vulnerabilities.....                                                       | 4  |

| 2.1.1.     | Security-Violating Design Bugs .....                                                | 4  |

| 2.1.2.     | Microarchitectural Side Channels .....                                              | 4  |

| 2.1.2.1.   | “Classical” ISA-visible Timing Side Channels.....                                   | 4  |

| 2.1.2.2.   | Transient Execution Side Channels (TESs) .....                                      | 5  |

| 2.1.3.     | Side Channels at Physical Levels.....                                               | 6  |

| 2.2.       | Security Targets – Confidentiality and Integrity.....                               | 6  |

| 2.3.       | Threat Models .....                                                                 | 7  |

| 3.         | State of the Art – Formal Hardware Verification Methods and Methodologies.....      | 9  |

| 3.1.       | New Era in Hardware Security.....                                                   | 9  |

| 3.2.       | Formal Verification for Functional Correctness .....                                | 10 |

| 3.2.1.     | Formal Verification without Property Specification - Automatic Linting .....        | 10 |

| 3.2.2.     | Formal Property Checking .....                                                      | 12 |

| 3.2.2.1.   | The Unbounded Paradigm.....                                                         | 12 |

| 3.2.2.2.   | The Bounded Paradigm .....                                                          | 13 |

| 3.2.2.2.1. | Bounded Model Checking .....                                                        | 13 |

| 3.2.2.2.2. | Advanced Methods of the Bounded Paradigm.....                                       | 14 |

|        |                                                                           |    |

|--------|---------------------------------------------------------------------------|----|

| 3.3.   | Theorem Proving .....                                                     | 16 |

| 3.4.   | The Role of Abstraction in Formal Hardware Verification .....             | 17 |

| 3.5.   | Formal Security Verification by Targeting Non-Functional Properties ..... | 19 |

| 3.6.   | Language-based HW security .....                                          | 21 |

| 3.7.   | Formal Verification at the Hardware/Software Interface .....              | 22 |

| 4.     | Research Needs and Recommendations.....                                   | 23 |

| 4.1.   | Research Contributions to Open-Source Initiatives .....                   | 24 |

| 4.2.   | Research Challenge – Tools for Formal Security Analysis .....             | 24 |

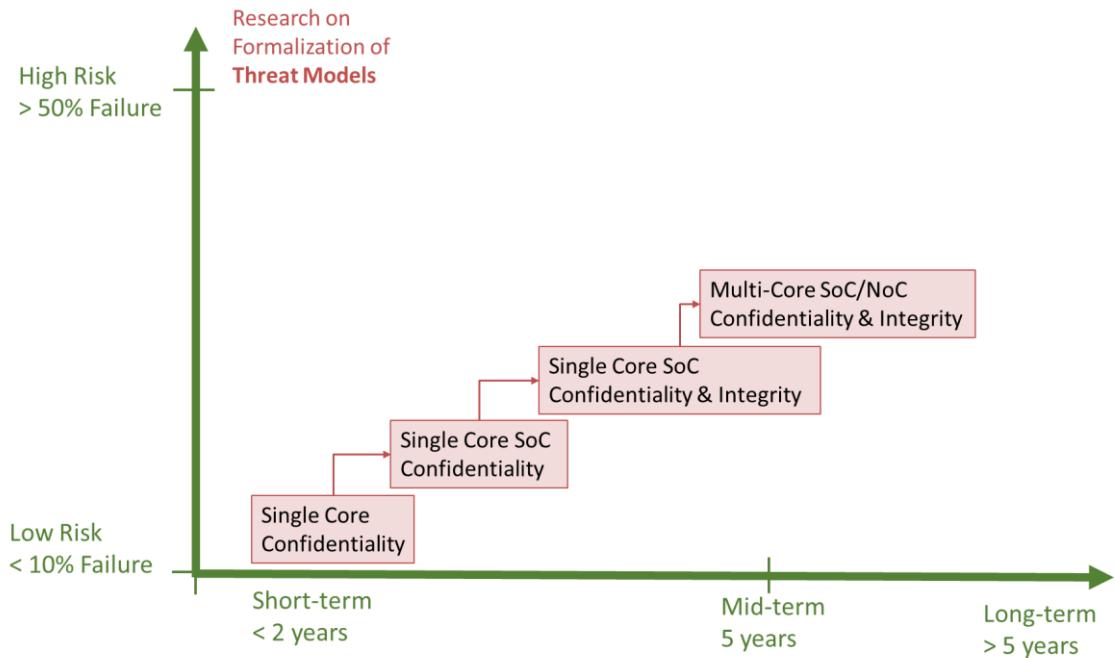

| 4.2.1. | Formalization of Threat Models .....                                      | 24 |

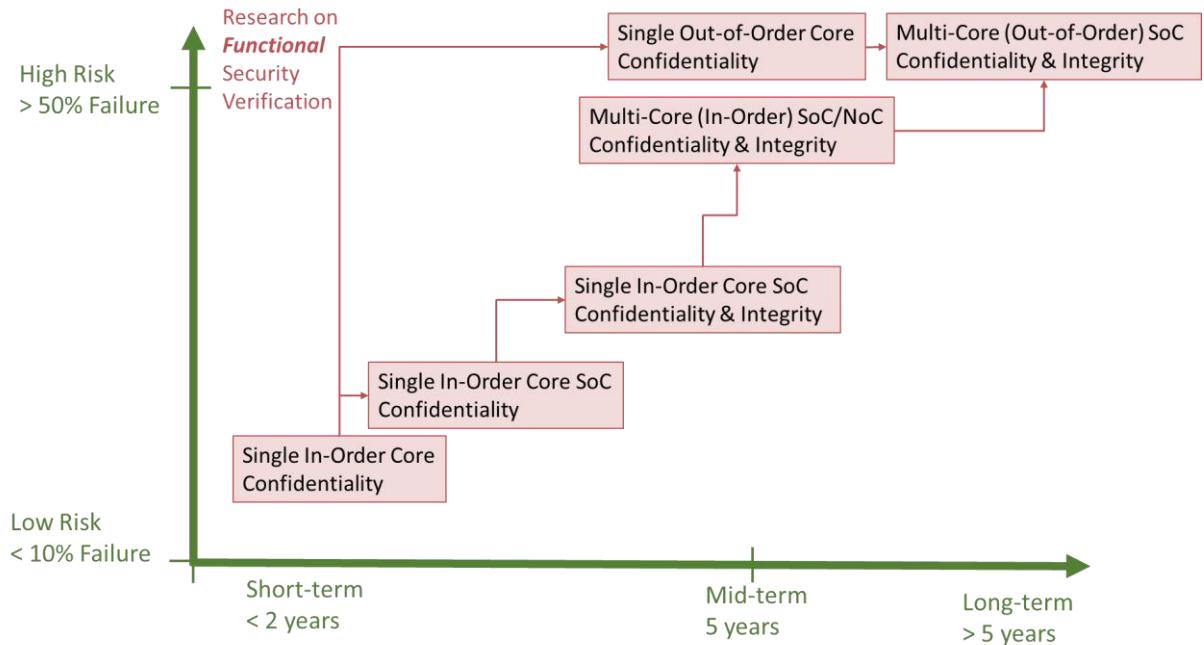

| 4.2.2. | Functional Verification for Avoiding Security-Critical Bug Escapes.....   | 25 |

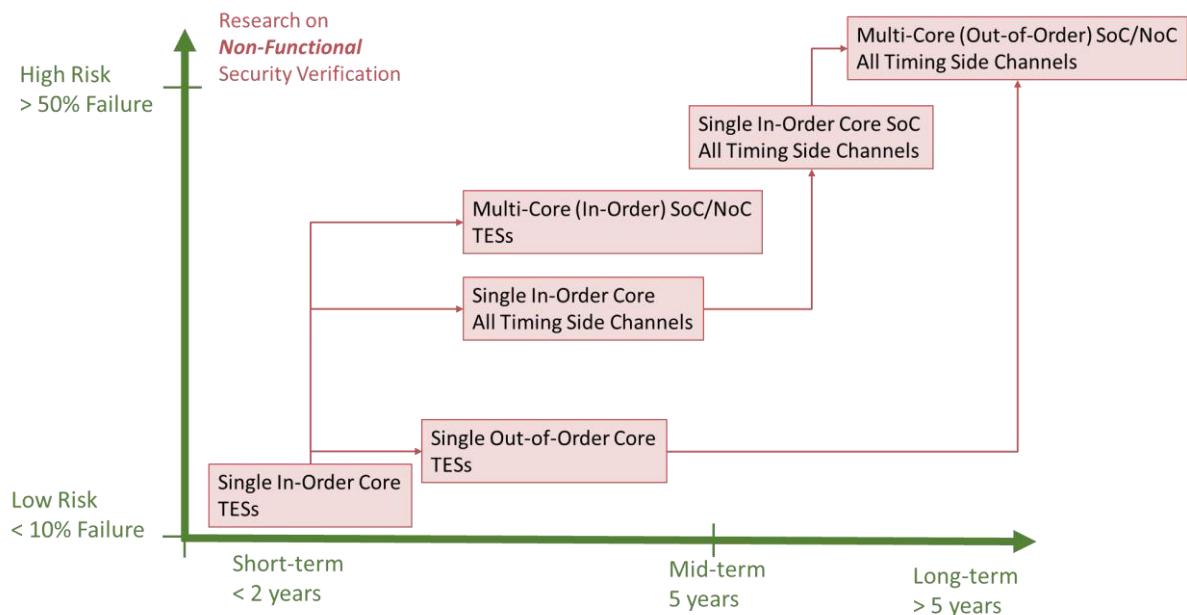

| 4.2.3. | Non-Functional Verification for Detecting Timing Side Channels.....       | 26 |

| 4.2.4. | Cost Estimate for Research .....                                          | 28 |

| 4.3.   | Research Challenge – Flow and Methodology .....                           | 30 |

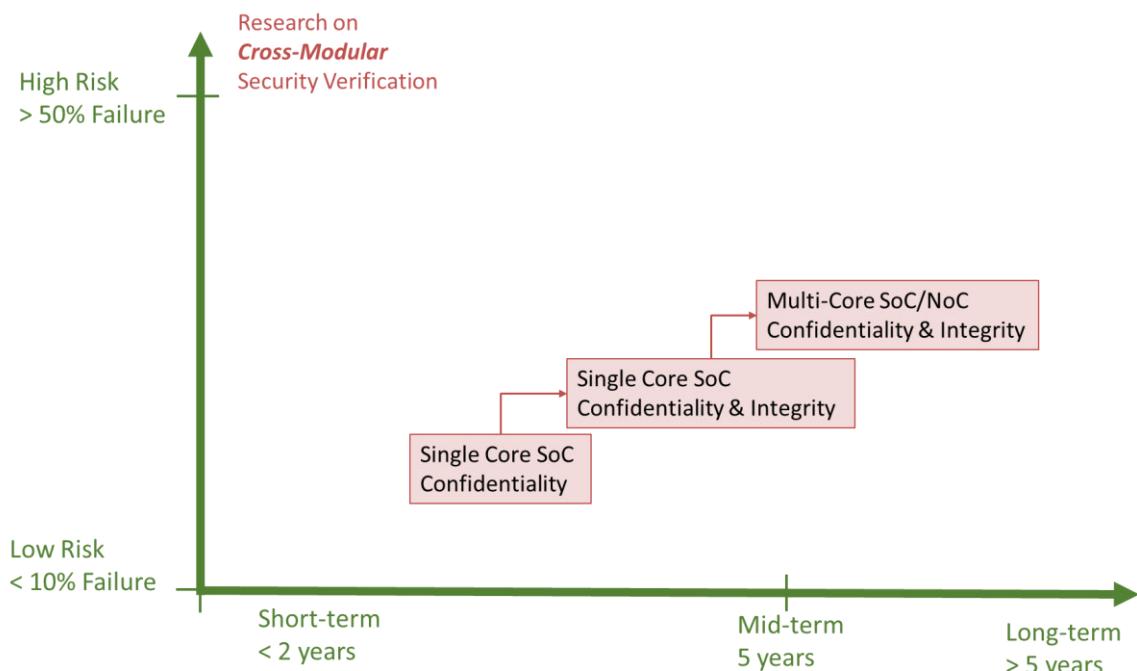

| 4.3.1. | Cross-Modular Security Flow – Horizontal Dimension.....                   | 30 |

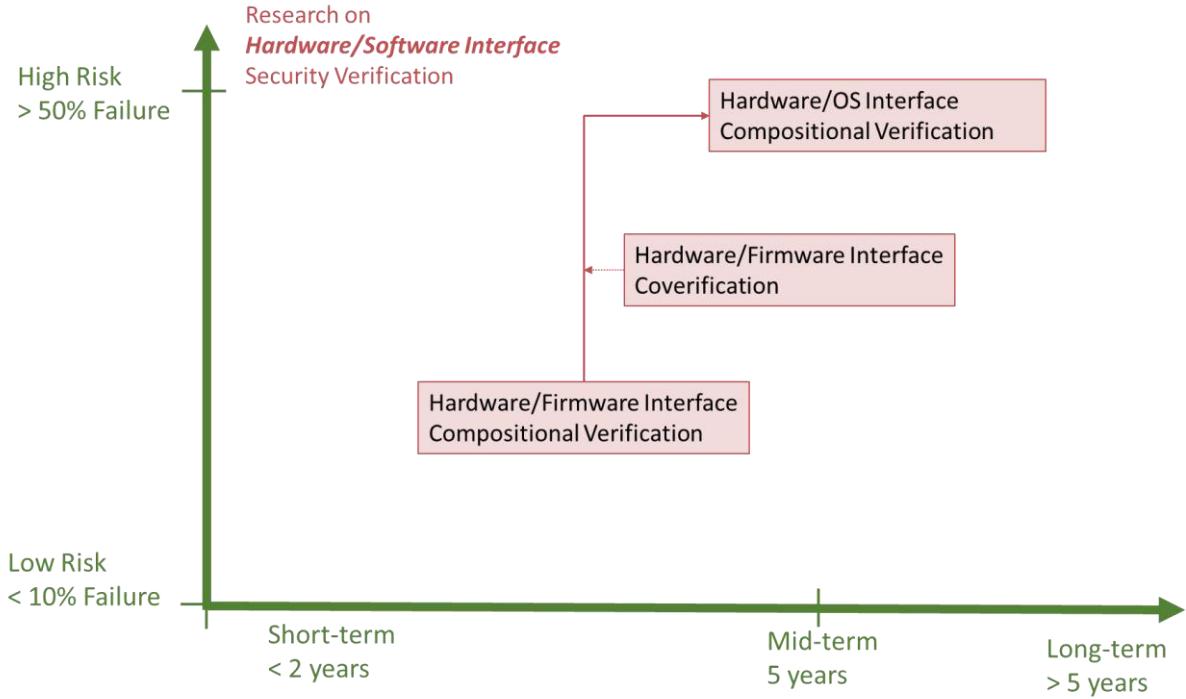

| 4.3.2. | Hardware/Software Interface – Vertical Dimension.....                     | 31 |

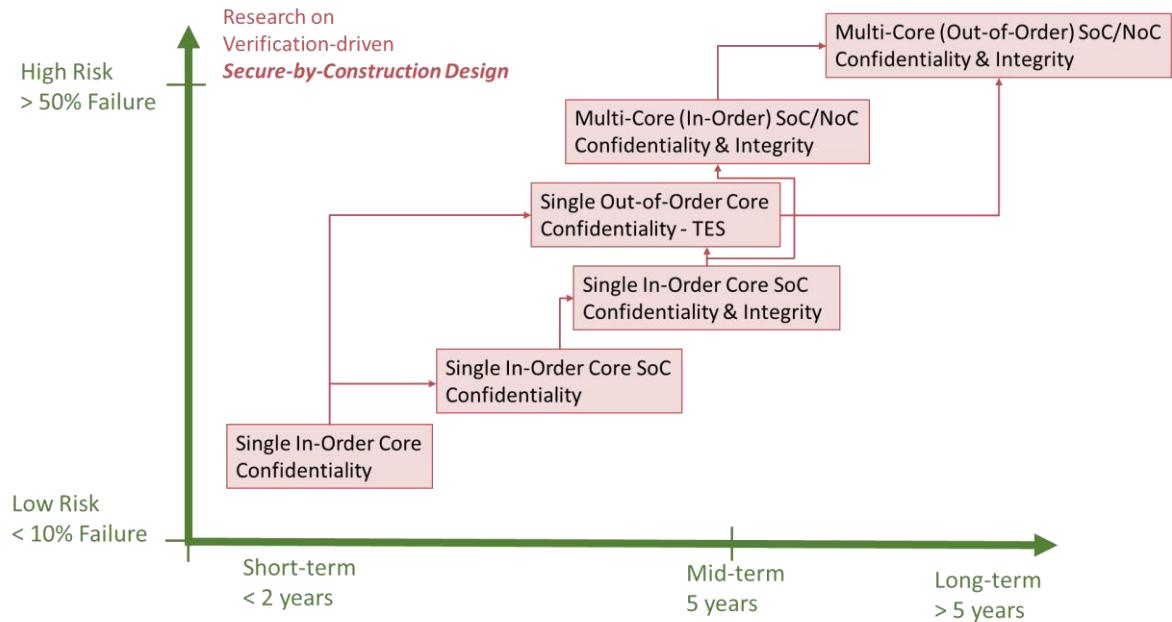

| 4.3.3. | Verification-Driven Design – Secure-by-Construction Design.....           | 32 |

| 4.3.4. | Cost Estimate for Research .....                                          | 33 |

| 5.     | Literature .....                                                          | 35 |

## 1. Introduction – Microarchitectural Security of Hardware

Ever since the invention of the first microprocessor in 1971, our society's reliance on electronic computing systems has been increasing at an accelerating pace. Computing systems ranging from small embedded systems to high-end server computers are part of the critical infrastructure for almost all industrial sectors, governmental and public institutions as well as for private life. System-on-Chips (SoCs) and embedded systems are ubiquitous in the modern society; with their abundance of connectivity features they create a new attack surface for cyber-attacks.

Our trust in computing systems, whether it regards the proper functioning of a power grid or the confidentiality of industrial data in edge computing, depends mainly on the provided safety and security features of the underlying computing system. Although the majority of the advanced security features, such as end-to-end encryption, are implemented at the software level, they rely on basic hardware primitives to deliver the intended functionalities. For example, encryption can be rendered useless if the hardware system does not provide a secure memory isolation ensuring the confidentiality of the encryption keys. In common terminology, such hardware primitives form the “*root-of-trust*” of the computing system. They constitute a set of trusted functionalities to ensure the security of the system. Design verification of these hardware parts is especially critical. Any security flaw in the hardware root-of-trust can affect virtually all applications deployed on the system.

Hardware systems are difficult or, in some cases, even impossible to patch, which exacerbates the challenge of dealing with hardware security flaws. Countless reports in recent years on system vulnerabilities at the hardware level, e.g., [1], [2], attest to the fact that hardware security flaws can pose a genuine threat to the overall system security. The Common Weakness Enumeration database (CWE) [3] has acknowledged this problem by including hardware vulnerabilities as a separate category of security weaknesses.

The role of hardware in system security is not limited to providing security-related features to support software functions. Weaknesses in the hardware design itself can introduce severe vulnerabilities to the computing system. At the microarchitectural level, these weaknesses mostly have two sources: the hardware circuit executing a security-critical software application may leak confidential information through side channels, in particular timing of the software execution [4], or (possibly very subtle) design bugs escape conventional verification procedures and cause security risks for the entire system.

In this Lot, we focus on the formal verification of hardware security requirements at the *microarchitectural level*. Microarchitectural descriptions at the Register Transfer Level (RTL) are the point of reference for sign-off verification before the tape-out of a chip for manufacturing. Therefore, RTL descriptions of the microarchitecture typically serve as the *golden model* of an SoC and are the basis for all design refinements at lower levels as well as for manufacturing. Security issues at these lower levels, especially those related to the supply chains, are subject to Lot 4.

## 2. Security Goals – Microarchitectural Security Risks and Verification Objectives

Formal security verification at the microarchitectural level requires well-defined verification targets covering all security risks or *threat models* that are relevant for a chip's intended deployment domain. A threat model reflects the global security requirements for a system, such as confidentiality and integrity and the “*attacker profile*” describing the capabilities of a potential attacker to interact with the system and to attack a certain category of vulnerabilities. The appropriate formalization of the relevant threat models, i.e., the specification of properties to be verified, is one of the main challenges in security research.

In the following, we provide an overview on security vulnerabilities in hardware, common security targets and the role of threat models. While security vulnerabilities are inherent to the design under verification, security targets and the profile of a potential attacker must be defined by the verification engineer based on knowledge about the environment in which the chip will operate.

## 2.1. Security Vulnerabilities

Formal security verification must address a wide spectrum of potential security HW vulnerabilities. In the following, we consider these vulnerabilities and related verification challenges. At the microarchitectural hardware level, there are two main categories of hardware vulnerabilities that can be distinguished: *security-violating design bugs* and *microarchitectural timing side channels*. In the latter category, so called *transient execution side channels* have recently received great attention.

### 2.1.1. Security-Violating Design Bugs

Security-violating design bugs are the subset of all design bugs that, besides violating the functional specification, violate a relevant security target. These bugs corrupt, for example, the functionality of memory protection mechanisms or some advanced security feature like information flow tracking. Throughout this study, the discussion of functional design bugs holds (unless noted otherwise) also for trojans present in the RTL (cf. Sec. 3.2.2.2). Trojans inserted *after* RTL sign-off, however, require additional measures. This is subject of the study for Lot 4.

In principle, security-critical design bugs (and RTL trojans) can be detected by conventional functional verification. However, this requires the complete and correct specification of the entire design as well as of all its security mechanisms. Substantial effort is demanded from verification engineers to cover all security-relevant functional behaviors by a set of properties. In many practical settings, this effort is considered prohibitively large, especially, since it is not sufficient to restrict this exercise to only the processor. Also all peripherals must be covered. Even when all modules of an SoC have been treated, verification gaps may still remain: Since functional properties are usually formulated locally for individual SoC modules, security issues related to the communication between modules or to the interaction between hardware and firmware are easily missed [5]. The challenges of the *functional verification paradigm* to security verification are further discussed in Sec. 3.2.

### 2.1.2. Microarchitectural Side Channels

The problem of side channels in hardware has been subject to research already for decades. It has been understood that the same degrees of freedom that a designer may use for optimizing a design at the microarchitectural level may lead to side effects that can be exploited in security attacks. At the microarchitectural level, side channels are based on timing. Although a program may not have access rights to a certain set of data, depending on this data, one and the same program may behave slightly differently in terms of its own computation results, i.e., what data it stores in which registers and at which time points. These differences only affect the detailed timing of the microarchitectural implementation and have no impact at the level of the *instruction set architecture* (ISA), i.e., they do not affect the correct functioning of the program as seen by the programmer. However, if these subtle alterations of the program's execution at the microarchitectural level are caused by secret data to which the program must not have access, this may open a "side channel". An attacker, owning (and creating) such a program, may trigger and observe these alterations to infer secret information. This is called a "microarchitectural side channel attack".

#### 2.1.2.1. "Classical" ISA-visible Timing Side Channels

Generally, in microarchitectural side channel attacks, the possible leakage of secret information is based on a microarchitectural resource that creates a timing information channel between different software processes that share this resource. For example, the cache can be such a shared resource and

an attacker can observe timing variations when accessing the cache based on the victim's cache access pattern. Various cache-based attacking schemes have been reported which deduce critical information from the footprint of an encryption software on the cache [4], [6], [7], [8], [9]. Also, other shared resources can be (mis-)used as the channel in a side-channel attack, as has been shown for DRAMs [10] and other shared functional units [11].

The following observation is key to classifying microarchitectural side channels and the corresponding verification targets (properties): In the attack scenario described above, the attacker process by itself is not capable of controlling both ends of a side channel. In order to steal secret information, it must interact with another process initiated by the system, the "victim process", which manipulates the secret and "makes a noise". In addition, the attacker must possess detailed knowledge about the victim software in order to make a meaningful correlation between the observed side channel and the victim's secret assets. Because of these prerequisites, the scope of a side channel attack may be limited to specific software components. While the detection and removal of such side channels in hardware may be beneficial in certain cases, possible defense mechanisms can benefit from their visibility at the ISA level and may rely exclusively on remedies at the software level (cf. Lot 1 and 3). Such remedies are typically applied to security-critical software components like encryption algorithms. Common measures include constant-time encryption [12] and cache access pattern obfuscation [13]. They prohibit the information flow at the "sending end" of the channel, i.e., the one owned by the victim process.

Although securing encryption software against these attacks is challenging because it demands a deep understanding of microarchitectural details, in the past, the threat of microarchitectural side channels was generally perceived to be limited to a small set of software applications. This general intuition, however, was drastically changed by the discovery of *transient execution side channel (TES) attacks*.

#### 2.1.2.2. Transient Execution Side Channels (TESs)

Despite using similar channels for exfiltrating information, TES attacks are fundamentally different from classical microarchitectural side channels. TES attacks exploit side effects of transient instruction execution, a phenomenon not visible in the sequential execution semantics of the ISA. Similarly like a factory attempts to maximize its productivity by keeping all its machines running as much as possible, modern processors attempt to maximize the use of their hardware units to achieve highest possible computing performance. Therefore, processors can reschedule the instructions of a program and may "transiently" execute instructions ahead of time, without ensuring whether or not the flow of the program actually reaches those instructions. If such "speculation" turns out to be wrong, i.e., the transiently executed instructions are not part of the correct program flow, the processor discards their results.

In a TES attack an attacker exploits advanced microarchitectural features, such as speculative execution or out-of-order execution, to transiently execute a sequence of instructions. This transient instruction execution may leak secret data through timing side channels and is the root cause for TES attacks. Without affecting the ISA-level results of the program, the attacker triggers transient executions of instructions that depend on secret data. In this way, the attacker does not rely on a vulnerability within a victim software to make a noise. In fact, the TES attacker controls both ends of the channel, the part that triggers the side effect and sends out the information as well as the part that observes it. This makes TES attacks more threatening than the earlier known timing side channels of Sec. 2.1.2.1. In the TES scenario, a single user-level attacker program can establish a microarchitectural side channel leaking parts of the memory which are not accessed by any other program. Such HW covert channels not only can destroy the usefulness of encryption and secure authentication schemes but can steal data from essentially anywhere in the system. As a result, unlike classical side channel attacks, TES attacks threaten the overall security of the system and its root of trust.

The first TES attacks to be discovered were Spectre [14] and Meltdown [15] which made world-wide headlines in 2018. The variety of attacks using TESs discovered since then (e.g., MDS attacks [16], [17], [18]), speculative store bypass [19], speculative interference [20]), with many of them targeting a previously patched system (e.g., Fallout attack [16]), has proven that the threat by TESs is not limited to Spectre and Meltdown and generally calls for new attention towards hardware security.

### 2.1.3. Side Channels at Physical Levels

Also side channels related to the physical implementation of a chip can cause severe concerns. This is true in particular for power side channels [21], [22]. Note that techniques of formal hardware verification, at least in their present form, operate at the logic design levels, typically at the RTL or above. Therefore, only little research has been reported how formal methods can contribute a mitigation of physical-level weaknesses.

Attacks at the physical level extract functional or non-functional information from analog signals. Checking whether or not secret information can be leaked therefore calls for methods operating at the physical or analog levels of the system. Formal analog verification, however, is in its infancy. Digitizing analog signals to make them suitable for conventional (digital) formal verification creates problem instances of enormous complexity. Instead, formal methods can have promise when applied to verify defense mechanisms that are implemented at the logical level, such as masking [23] or balancing [24]. This may result in specialized methods that can be integrated into a verification flow for security, as discussed in Sec. 3.5. Abstracting from physical behaviors, however, bears the risk of missing security gaps that are not modeled by the formal tool, for example, as demonstrated by [25] for the work of [26].

In summary, while new and promising ideas may be emerging, the question whether or not formal hardware verification can be a general new research area for physical-level side channel detection is of speculative nature. It is therefore not further elaborated in this study.

## 2.2. Security Targets – Confidentiality and Integrity

*Confidentiality* and *integrity* are commonly considered the most relevant security targets for hardware. In the software domain it is common to also consider *availability* as a third security target. In the hardware domain it is common to subsume this notion under *integrity*, as becomes apparent from the following discussion.

*Confidentiality* of hardware is given if all information stored or processed in the system is protected against being retrieved by an unauthorized entity.

*Integrity* means preventing an attacker from changing or influencing a part of the system that is specified as protected. Similarly as in the software domain, where integrity forbids the unauthorized modification, deletion or insertion of data, we can understand integrity in hardware as the *integrity of information*. Specifically, this means that a set of protected registers and memory locations cannot be overwritten by an unauthorized entity. Since hardware, as opposed to software, is a physical system, the notion of integrity is commonly defined to have a wider scope. Attackers with physical access to the system may influence the system physically, for example, by manipulating voltage levels or by other physical fault injection techniques. Therefore, besides the *integrity of information* there is another relevant class of integrity goals in hardware which we can subsume under the notion of *integrity of operation*. Integrity of operation is maintained if an untrusted entity cannot change the result or timing of a protected *operation* in the system. Note that this also includes the *availability* of security-critical functional resources.

Besides physical attacks, another relevant threat to the integrity of hardware results from the integration of third-party components into the system. Intellectual Property (IP) modules from

untrusted sources bear the risk to maliciously influence security-critical operations of protected SoC components.

Further security targets may be of importance and are often considered as subordinate goals of confidentiality and integrity. We provide two examples:

#### Authenticity

Authenticity ensures the correct identification of communication partners as well as the authenticity of data. This is achieved by a verifiably correct authentication process determining whether the credentials given by a user or another system component are authorized to access the resource in question.

#### Privacy

Privacy refers to the objective to keep some or all processing of a system user secret to the rest of the system. This may involve the anonymity of the user. Verifiable measures for privacy include for example cryptographic techniques and trusted execution environments [27], [28]. The correctness of HW/SW interaction usually plays a major role when ensuring privacy.

### 2.3. Threat Models

A threat model for hardware captures the security requirements for a system in combination with a profile of the attackers. The attacker profile makes assumptions about how attackers can access the system and what methods they can use to exploit potential vulnerabilities of the system. For example, an attacker may access the system by running an unprivileged user process. Another threat model may consider access to the security-critical system through a third-party IP which is added to the system and which the attacker controls (cf. Sec. 2.2). Specific threat models are the basis for the specification of verifiable properties. The challenge consists in formulating these properties in such a way that a large spectrum of different threat models is covered by a manageable set of properties.

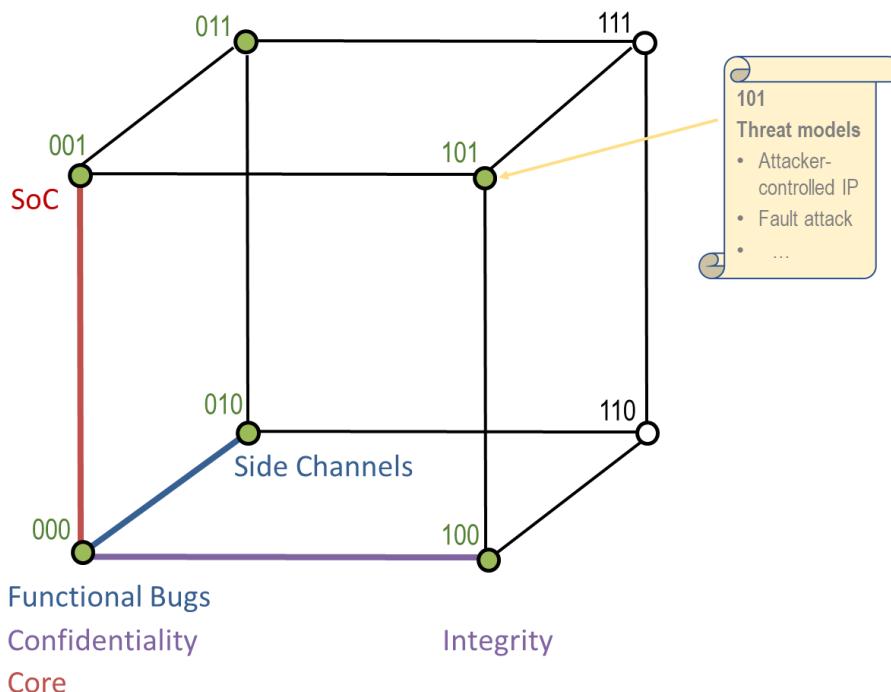

Figure 1: Space of threat models

Figure 1 illustrates the space of threat models that must be analyzed for specifying verifiable properties. The points associated with important threat models are marked in green color. Firstly, we must distinguish different kinds of security vulnerabilities. As elaborated in Sec. 2.1, it is meaningful to distinguish between security-violating functional bugs and non-functional vulnerabilities, in particular side channels. This is the blue dimension in the shown space. This distinction is reasonable since, by their definition, side channels are not detectable by any functional verification, such as conventional formal hardware property checking (cf. Sec.3.5). At the microarchitectural level, these side channels could be further divided in sub-classes such as TESs and other channels, as described in Sec. 2.1. For simplicity, we do not display these additional dimensions and restrict the illustration of

Figure 1 to a three-dimensional cube.

*The vertical dimension (red color) of the cube in*

Figure 1 distinguishes between vulnerabilities that occur only in *cores* and those requiring a global analysis of the entire *System-on-Chip (SoC)*. For example, TESs, such as Spectre and Meltdown, only require an analysis of the core while the root cause of other types of timing side channels can be distributed over several locations of the SoC. The distinction along this vertical dimension has a large impact on the kind of formal analysis that must be performed. While specialized methods exist specifically for cores, the analysis of the entire system demands more complex procedures typically based on compositional principles.

Thirdly, the horizontal axis of the cube separates threat models related to the security target of *confidentiality* from those related to *integrity*. While there exist well-defined notions of confidentiality in hardware, the formalization of hardware integrity can be more demanding and requires a careful analysis of the attacker profile relevant for the hardware's intended deployment domain. For example, in some scenarios a primary concern results from the integration of untrusted third-party IPs into an existing and trustworthy platform. In other scenarios, such as chipcard applications, fault attacks (e.g., by laser light) corrupting the system can be of particular concern.

*We give some examples of threat models related to specific points of the cube in*

Figure 1:

❖ **Point 010**

Threat Model 010

|                           |                                                                     |

|---------------------------|---------------------------------------------------------------------|

| Security target:          | Confidentiality of data in protected memory locations               |

| Attacker Profile:         | Attacker can run any program on the core with user-level privileges |

| Class of vulnerabilities: | Transient Execution Side Channel in cores                           |

❖ **Point 011**

Threat Model 011

|                           |                                                                     |

|---------------------------|---------------------------------------------------------------------|

| Security target:          | Confidentiality of data in protected memory locations               |

| Attacker Profile:         | Attacker can run any program on the core with user-level privileges |

| Class of vulnerabilities: | ISA-visible timing side channels in core or peripherals             |

❖ **Point 001**

Threat Model 001

|                           |                                                                                                |

|---------------------------|------------------------------------------------------------------------------------------------|

| Security target:          | Confidentiality of data in protected memory locations                                          |

| Attacker Profile:         | Attacker can run any program on the core and can access peripherals with user-level privileges |

| Class of vulnerabilities: | Functional design bugs (or trojans)                                                            |

*Note that several threat models can belong to each point in the space of*

Figure 1, for example:

❖ **Point 101**

Threat Model 101a

|                           |                                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------|

| Security target:          | Integrity of information and integrity of operation in security-critical parts of SoC       |

| Attacker Profile:         | Attacker controls a third-party IP which communicates with the security-critical SoC domain |

| Class of vulnerabilities: | Design bugs (insufficient protection mechanisms)                                            |

Threat Model 101b

|                           |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Security target:          | Integrity of information and integrity of operation in security-critical parts of SoC |

| Attacker Profile:         | Attacker can inject faults by laser light anywhere in the SoC                         |

| Class of vulnerabilities: | Design bugs (insufficient protection mechanisms)                                      |

Threat Model 101c

|                           |                                                                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Security target:          | Integrity of information and integrity of operation in security-critical parts of SoC                                             |

| Attacker Profile:         | Attacker can inject faults by laser light anywhere in the SoC and can run any program on the main core with user-level privileges |

| Class of vulnerabilities: | Design bugs (insufficient protection mechanisms)                                                                                  |

It is the task of the hardware security engineer to conduct a threat analysis for the considered design. The result of this analysis is a set of threat models that are relevant for the considered design and its deployment domain, such as illustrated by the above examples. The derived threat models are the basis for the verification engineer to define the verification targets. A set of properties to be verified is used for each threat model. A key challenge for the verification methodology is that the engineer must develop a full understanding about what threat models can be covered by specifying which properties. This means the engineer must understand for which security targets the developed properties provide guarantees, under what assumptions for the potential vulnerabilities and for which profile of the attacker.

Modern property languages, such as SVA, provide a strong basis for formalizing the threat models described above. Besides the language, however, the general verification methodology has a strong influence on how property sets with appropriate coverage are specified. The state of the art in these methodologies is subject to the following section.

### 3. State of the Art – Formal Hardware Verification Methods and Methodologies

#### 3.1. New Era in Hardware Security

For better understanding the evolution of formal hardware verification in the field of microarchitectural security, it is helpful to pay particular attention to recent developments in the field.

In the context of cybersecurity, formal methods have particularly strong roots in the software domain. This has mainly two reasons: First, a large body of security violations in IT systems is based on software deficits; and formal methods to mitigate these weaknesses have been under intensive research for decades. Second, as elaborated in Sec. 2.1.2.1, many vulnerabilities that exploit hardware weaknesses, such as cache-based side channels, could mostly be addressed by software defenses.

In other words, a software-driven view on microarchitectural hardware security dominated the field for many years. However, this changed abruptly in January 2018 when headline news about the discovery of new hardware attacks called Spectre and Meltdown startled the general public around the globe. The industry reacted promptly and swift software updates were provided. However, they offered only little relief. It was quickly understood that Spectre and Meltdown belonged to a new class of ISA-invisible side channels, further explained in Sec. 2.1.2.2. A keynote statement of David Patterson (IEEE/ACM Design Automation Conference, 2018), co-inventor of modern RISC computer architectures and Turing Award winner 2017, underlines this insight: *“State of computer security is embarrassing for all of us in the computing field. It seems unlikely systems will ever become secure using software-only solutions”*.

It turns out that Spectre and Meltdown are only two examples of a larger class of new side channels which were named “transient execution side channels (TES)” (cf. Sec. 2.1.2.2). Almost on a monthly basis, new types of attacks of this class were discovered and reported. The variety of such attacks discovered in recent years ranges from MDS attacks (e.g., [3]) to Speculative Interference [4], with many of them successfully attacking a previously patched system (e.g., Fallout attack [3]). The initial hope for short-term and full solutions to defend against these new weaknesses were not fulfilled, as admitted by Martin Dixon, VP for Security at Intel: *“The potential for a transient execution to extract data being carried across a branch or a load is still a new field of research. Even though transient execution attacks are highly complex and difficult to carry out successfully outside of a lab, we expect it to remain a persistent focus area for researchers and the computer industry.”*

Today, re-establishing trust into the microarchitectures of computing systems has become one of the main goals in the computer industry and among chip makers. Security verification and the development of defense mechanisms at the *hardware* level have become rapidly growing research fields and complement activities at the software level. There is general conviction that the formidable patch-and-pray cycles can only be overcome if comprehensive security guarantees are already provided during the design phase and when signing-off a chip before tape-out. Formal verification bears promise to provide such guarantees. However, while it is encouraging that formal methods have become mainstream in many industrial flows for hardware design, most of these techniques are tailored towards general functional design aspects and suffer from severe limitations when targeting microarchitectural security and side channels.

In the following, we first consider mainstream formal verification techniques, as they have been developed for checking the functional correctness of a design (Sections 3.2, 3.3, 3.4). They provide the basis for detecting security-critical design errors. Then, we describe the state of the art in techniques specifically targeting security (Sections 3.5, 3.6). The role of the formal hardware verification at the hardware/software interface is described in Sec. 3.7.

### 3.2. Formal Verification for Functional Correctness

This section summarizes basic concepts and the state of the art in common approaches to functional verification with formal methods. We compare the different classes of techniques qualitatively in terms of three important criteria for any formal method: *scalability*, *degree of automation* and *coverage*.

#### 3.2.1. Formal Verification without Property Specification - Automatic Linting

“Automatic formal verification” of hardware, i.e., formal verification without the need of specifying verification targets by some property language, historically often served as the “appetizer” to formal methods and guided industry into a more elaborate use of formal techniques. Commonly, this class of methods, also referred to as “hardware linting”, is used to check RTL design rules that must be fulfilled for *any* design, independently of its specific function. Hardware linting targets poor coding styles,

mismatches of the simulation and synthesis semantics in the RTL code, coding errors in finite state machine (FSM) implementations and similar issues. A particular focus often lies on detecting problems related to the synchronization of clocks and clock domain crossings.

Automatic linting is a standard feature in many commercial tools and is typically employed as a precursor to more advanced verification efforts, as described below. There is currently only little research on formal hardware linting in academia. Notable exceptions exist which, however, address advanced methods of formal verification that largely avoid the formalization of the design's functionality. Instead of simple design rules, sophisticated but still generic design properties are investigated. Examples of such advanced linting methods are the work of [29], [30], [31] for checking functional correctness in processor cores and of [32] for checking clock-domain crossings in very large designs.

Scalability: Checking design rules often does not require a deep logical analysis of the design or even a traversal of the system's state space. This holds, for example, if only structural conditions regarding design connectivity or coding rules are checked. Therefore, scalability of hardware linting techniques is usually very high. Entire chips can be analyzed in a single run. For more advanced approaches checking functional behavior in more depth, similar limitations apply as discussed below for property checking. In fact, the advanced techniques of hardware linting are often based on the property checking methods discussed below.

Degree of Automation: A high degree of automation is a clear differentiator of linting techniques compared to other verification techniques. In most cases, the properties are checked fully automatically.

Coverage: The beneficial characteristics of hardware linting with respect to scalability and automation come at the price of relatively poor coverage. Design-specific properties cannot be checked. Hence, this class of techniques never guarantees compliance of an implementation with a design-specific specification.

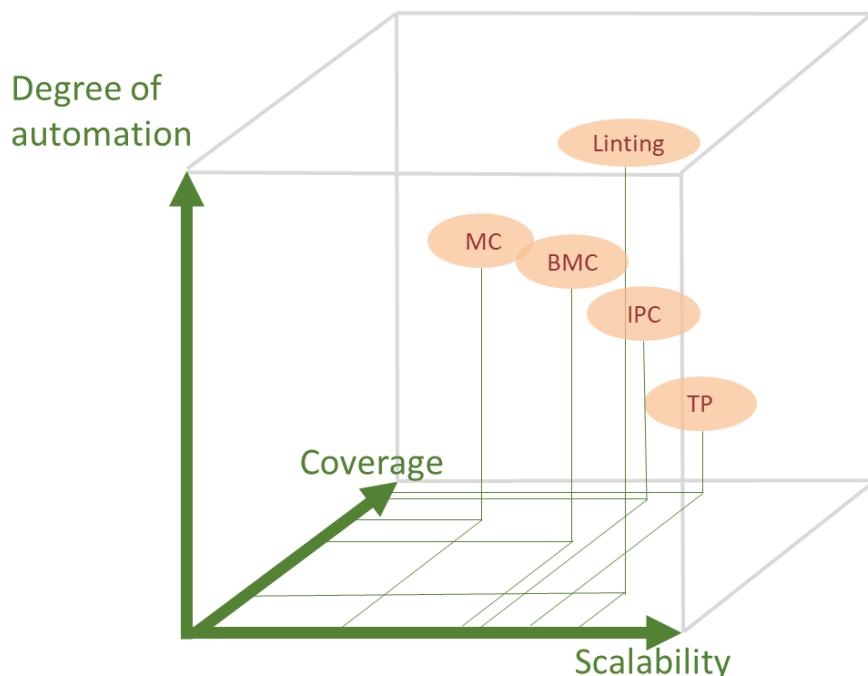

The trade-off between these criteria is illustrated in Figure 2 by the mark for "Linting".

Figure 2: Qualities of methods of formal hardware verification

### 3.2.2. Formal Property Checking

In *property checking* a design model is checked against a functional specification using formal and automatic methods. The design model can be given at different levels of abstraction. In most industrial settings of hardware design, it is mainstream to use RTL models, typically given as VHDL or Verilog descriptions, as the basis for verification. Additionally, also descriptions at higher abstraction levels based on languages like SystemC gain popularity in the verification flow. The choice of a model and a level of abstraction have a large influence on what verification targets can be addressed. Models at a high level of abstraction allow for handling large designs but miss relevant information, for example, the clock-accurate timing of a microarchitectural implementation. Many security gaps, such as TESs, can only be detected by an analysis that operates on a model which is both bit- and clock cycle accurate. Therefore, the following discussion concentrates on formal verification at the RTL which is also the standard for SoC sign-off. The challenge of using abstraction levels above RTL in security verification is further discussed in Sec. 3.4.

The functional specification is often provided in an informal way using textual descriptions, flow charts, timing diagrams and the like. The main manual effort in formal verification by property checking results from the task to formalize this specification in terms of properties. Importantly, the properties must be written in such a way that the possibly wrong thinking of a designer and related implementation bugs are not imported into the property specification as well. This is accomplished by adopting a property specification style that describes the functional behavior abstractly and without restrictions regarding its implementation. Similar like the ISA specification of a processor denotes the behavior of a processor instruction in terms of programmer-visible registers and without any consideration of *how* this behavior is implemented (e.g. in-order pipeline or out-of-order pipeline), the property specification for hardware should only describe *what* functional behavior is expected but not *how* it is implemented. SystemVerilog Assertions (SVA) is currently the most popular language for specifying properties at the RTL.

The way how properties are formulated to specify the relevant verification targets is critical for the quality of the overall verification results. The question arises what properties shall be written and to what extent the functional behavior of a design is *covered* by a given property set. Different coverage metrics are available to answer these questions. Often, coverage in formal verification adopts concepts from simulation-based verification. Especially mutation analysis is commonly used. Faults are injected into the design to systematically generate design “mutants” and it is checked what fraction of these errors is discovered by the given property set [33], [34]. Other coverage metrics for formal methods address the completeness of the specification [35], [36], [37]. In general, *coverage* is a main concern in every verification flow and differentiates verification approaches from each other.

A formal property checker exhaustively evaluates a given property on the given model. This is the task of the underlying *proof method*. The proof method should be as automatic as possible and in many cases is indeed fully automated. The main criterion for the quality of the proof method is typically its scalability on large designs.

Scalability, degree of automation and coverage are the main differentiators between different approaches to property checking. The possible trade-offs between these three criteria have led to the development of two main classes of formal proof methods pursuing the *unbounded* or the *bounded paradigm* of property checking. The trade-offs associated with these paradigms are elaborated next.

#### 3.2.2.1. The Unbounded Paradigm

The Unbounded Paradigm denotes the classical approach to formal verification by property checking. Invented already in the 1980s, *model checking* [38], [39], [40], [41] lays the foundation for many of today’s formal verification methods both for hardware and for software. Both hardware and software

can be represented in a uniform way by well-defined sequential models. In model checking a sequential model's compliance with a temporal logic expression, the “property”, is evaluated by formal and fully automatic methods. Model checking reasons on sequential models with a finite number of internal states and considers behaviors over infinite times. This allows for proving strong guarantees on a design. Modern algorithms for model checking often rely on data structures based on Binary Decision Diagrams (BDDs) [42]. BDDs are graph representation of Boolean functions and provide a powerful instrument to represent the large state space of a sequential model in a compact and manageable way.

#### Scalability:

Scalability is the main limitation of the unbounded paradigm. Model checking for today's hardware designs requires the traversal of huge state spaces. Substantial progress in model checking based on advanced state space representations and automatic abstraction techniques make it possible to deal with state spaces of  $2^{\text{hundreds}}$  states. Although this is an astronomic number, it means that systems with up to a few hundreds of state variables can be handled. Note, however, that hardware modules of today's SoCs typically have *hundreds of thousands* of state variables. This limits the use of the unbounded paradigm to proving only local assertions in a design. In the context of security verification, the unbounded paradigm may be applied only to small SoC security elements. Therefore, in practice, the unbounded paradigm is often complemented with a methodology based on the *bounded paradigm*, described below.

#### Degree of Automation:

Conventional model checking techniques are fully automated. The only manual effort arises from the need of formulating the property. This effort depends largely on the considered verification tasks.

#### Coverage:

It is an advantage of unbounded model checking that the formulated properties can cover the specified behavior at all times during the existence of the system. This makes a strong contribution to coverage. However, coverage also depends on what properties have been formulated and how a set of several properties contributes to composing a proof with global guarantees [43]. This is a question of advanced methodologies whose adoption in practice has been hampered by the limited scalability of unbounded model checking. Therefore, in commercial practice, unbounded model checking is mostly used in the context of Assertion Based Verification (ABV) where designers sprinkle assertions into their code to build confidence into the design. Although commercial vendors support this process by certain (often proprietary) coverage-driven flows, the resulting coverage is often considered insufficient or remains unclear. In such a setting the bulk of the verification effort is therefore left to simulation.

The trade-off between these criteria is illustrated in Figure 2 by the mark for model checking “MC”.

### 3.2.2.2. The Bounded Paradigm

#### 3.2.2.2.1. Bounded Model Checking

Bounded Model Checking (BMC) [44] laid the foundation to the bounded paradigm in property checking. As the name suggests, in BMC the property checking problem is restricted to a finite bounded time interval. To this end, the temporal property is formulated for a finite time window starting from a known state of the system, often the reset state. This formulation has the great advantage that the reasoning on sequential systems can be mapped to the Boolean Satisfiability problem (SAT).

SAT is the problem to decide for a given Boolean function whether or not there exists a valuation to its variables such that the function assume the value '1', i.e., it is “satisfied”. BMC leverages the fact that tools to solve the SAT problem, so called “SAT-solvers”, have been a very active research field during the last two decades and very powerful solvers are available today, both in industry and in public domain.

In BMC the design and the property are converted into a Boolean function such that any valuation to its variables satisfying the function is a counterexample to the property. If the function is proven to be unsatisfiable, i.e., no counterexamples exist, the property is verified to hold for the given time interval and start state.

#### Scalability:

The scalability of BMC compares favorably with most other approaches in formal verification. Hardware designs with tens or even hundreds of thousands of inputs, outputs and internal state variables can often be handled within short proof times. Besides the size of the design also the nature of the property has an influence on the scalability of solvers. This is addressed by appropriate methodologies how properties are formulated. Different commercial providers support different flavors of such methodologies and provide guidance to the verification engineers to make best possible use of the available tools.

#### Degree of Automation:

The BMC proof techniques are fully automated. The only manual effort arising in BMC-based verification comes from the need to formulate properties. This effort depends largely on the considered verification tasks and is similar to most other property checking techniques.

#### Coverage:

Coverage is the main limitation of BMC. The functional behavior is analyzed only for a finite number of clock cycles starting from a well-defined state. Hence, there is no global proof of the property, only a “bounded proof” which guarantees correct behavior in a certain time window. On the other hand, BMC can be a very efficient tool to quickly detect counterexamples to a property. Therefore, in industrial practice, BMC quite often serves as a “bug hunting” method.

The trade-off between these criteria is illustrated in Figure 2 by the mark for model checking “BMC”.

#### 3.2.2.2.2. Advanced Methods of the Bounded Paradigm.

The limitation of BMC with respect to providing generally valid, “unbounded” proofs often motivates the use of more advanced methods under the bounded paradigm, such as Symbolic Trajectory Evaluation (STE) [45], Interval Property Checking (IPC) [46] and k-Step Induction [47]. All of them have in common with BMC that they consider behaviors within bounded time windows. However, they achieve unbounded proofs by additional concepts. K-step induction combines the local proofs over finite times with inductive reasoning. IPC and STE avoid induction but obtain unbounded proofs for properties formulated over bounded time windows by considering *any state* at the start of the time window. For example, this allows to prove that a processor instruction (executed over finite time) is correctly implemented at the RTL and complies with its ISA specification. IPC and STE have their roots in industrial developments. IPC was developed already in the 1990s within Siemens, the STE development has been driven mostly within Intel.

For the advanced methods of the bounded paradigm and IPC in particular, comprehensive case studies were conducted by German industry to assess the productivity and quality of the design and verification flow. This was compared with state-of-the-art simulation-based approaches. Some of these case studies were conducted by BMBF consortia [48], [49]. The gained insights can be summarized as follows:

#### Scalability:

Scalability turned out to be less of a problem than originally expected by industrial users. Similar as in BMC the advanced methods of the bounded paradigm map reasoning on sequential systems to combinational problems. Therefore, the scalability of their proof engines is similarly high as for BMC.

With few exceptions, the common verification targets of SoC modules can be proven without substantial problems. For example, large parts of the Infineon Tricore processor, a high-end processor for automotive applications were exhaustively verified by IPC [50]. Almost all properties of this design (with more than 130k lines of Verilog code) were proven, each within few minutes. This is even considered an advantage over simulation-based methods that often run for weeks on clusters of compute servers. Since then, in industrial design and verification projects conducted over the years, such results were confirmed on numerous other SoC modules of different nature, ranging from telecom and automotive to IoT applications.

#### Degree of Automation:

As in all other property checking methods manual effort is required to create the properties to be verified. In this aspect the advanced methods of the bounded paradigm differ only little from other methods of property checking. Due to the popularity of these approaches, however, investments have been made, especially in industry, to automatically generate the required properties from higher level models, such as within Infineon [51]. This reduces manual effort substantially. (It should be noted that this progress is not intrinsic to the nature of these proof methods itself. In principle, property generation can be combined also with any other approach to property checking.)

Compared to standard BMC, the advanced methods of the bounded paradigm, however, suffer from an additional source of manual effort. This effort is related to generalizing the bounded proof to infinite time. In IPC, for example, considering *any* state at the beginning of the time window is the root cause of *false alarms*. Counterexamples suggest a failing property but are based on starting states of the considered time window that are impossible in the design. The problem can be solved by excluding such “unreachable” states from consideration. This requires refining the starting state of the model by so called “invariants”. Identifying these invariants requires additional procedures and accounts for additional manual effort when employing this paradigm.

The productivity of a formal verification engineer covering a design’s entire functional behavior using IPC or related methods amounts to approximately 2000 lines of RTL code per person month, as measured in a number of industrial case studies [48], [49]. For specific modules, such as processor cores, this productivity can be substantially higher when properties are generated automatically [31].

#### Coverage:

Coverage is the strong side of the advanced methods in the bounded paradigm. This does not only result from the fact that the proofs obtained are unbounded. Additionally, systematic methodologies exist, especially for IPC, to derive sets of properties from the informal specification such that well-defined coverage metrics are met. The most advanced approaches [36], [37], [31] ensure with formal rigor that the developed property set uniquely determines the entire design behavior. In other words, two hardware designs fulfilling the same such property set are necessarily equivalent. Industrial case studies [48], [49] and today’s industrial experience confirm that a substantial number of design bugs can be identified by formal techniques which were missed previously by simulation.

□

In spite of the encouraging successes described above, formal verification remains a challenge in industrial practice. One of the main reasons is the effort for property specification. Although in terms of quantitative numbers this effort may not exceed the effort needed for simulation-based approaches, such as for developing testbenches, the different nature of formal techniques and simulation is quite essential. Simulation is mostly a black-box approach. The verification engineer must understand the specification but needs no knowledge about the internal architecture of a design. This has big advantages, for example, when outsourcing verification to external service providers. Formal

verification, by contrast, is a white-box technique; the verification engineer must understand internal design structures to formulate properties. This special expertise is not always available.

A common response to this problem consists in bringing verification closer to design, such as in commercially available Assertion-Based Verification (ABV) where the designers themselves insert assertions into the design. This is often considered a valuable addition to the design flow but does not fully replace the conventional simulation phase.

More recently, however, as safety- and security-critical applications are becoming more common in embedded computing, we can observe a renewed trend towards formal methods. More and more often, the extra costs for formal approaches are considered justified in view of the risks that otherwise are taken. According to the Wilson industrial survey [52] more than 40% of industrial chip design projects currently adopt formal methodologies.

Today, the state of the art in property checking for hardware is defined by commercial vendors such as Synopsys, Siemens EDA and Cadence. In contrast to the software domain, open source tools for hardware verification are rare. Partly, this can be explained by the complexity of design descriptions using hardware description languages. They support a wealth of features which impose high hurdles on creating a front-end technology for any tool. Developing a front end for state-of-the-art property checking demands a great and continuous development effort, while being rather unrewarding from a scientific point of view. Open source contributions are therefore mostly restricted to the backend solvers based on Satisfiability Solving (SAT) and Binary Decision Diagrams (BDDs). Notable exceptions are E-BMC (latest release in 2017) [53] and SymbiYosys [54]. These open-source tools provide multiple proof engines in their backend but support only a subset of SystemVerilog and SVA in the frontend. Important “quality-of-life features” like black-boxing are missing. SymbiYosys allows for extended functionality only for its commercial upgrade. The functionality supported in public domain does not allow for obtaining competitive results on realistic SoC designs. The limitations may partly result from a “chicken-egg” problem. Most academic research groups in hardware verification currently make use of the free (or low-cost) licenses for commercial tools which are superior to currently available open-source solutions. On the other hand, the quality of open-source tools might increase if there was a stronger demand from the research community.

### 3.3. Theorem Proving

Automated theorem proving is a subfield of mathematical logic concerning the automation of mathematical proofs. All of the techniques discussed for the formal verification of digital systems can therefore be considered automated theorem proving. However, it is useful to distinguish methods based on general purpose theorem provers—which are computer programs capable of assisting a variety of traditional deductive mathematical proofs – from the more specialized property checking techniques for hardware, as described above.

A number of theorem provers are available, differing in their emphasized problem domains and input languages. Most of them are freely available academic developments, e.g., HOL [55], Coq [56], and Isabelle [57]. Complex mathematical theorems have successfully been formalized and proven using theorem provers, including a few previously open problems, e.g., Kepler’s conjecture and the four color theorem [58].

A theorem prover requires a formalization of the problem under consideration in the syntax of the tool’s language. The computation of the proof is automated as part of an interactive process where axioms and reasoning techniques are specified. Verifying digital hardware based on a general-purpose theorem prover is actually a demanding process. It requires knowledge on proofs of classical

mathematical theorems and, even more critically, expertise to correctly formalize the design and verification target in a representation accepted by the tool.

Yet, industrial activities in theorem proving are alive. After the infamous Pentium FDIV bug [59] especially floating-point units have been granted the attention of such rigid formal methods. Larger chip makers and companies with particularly high requirements on hardware quality support in-house expert teams on theorem proving to support the high end of their verification flows.

Scalability: The scalability of theorem provers can be considered high. They can leverage essentially the full state of the art of proving methods that match the given model and verification target. In addition, theorem proving benefits from the possibility to build a sound stack of models. This is further discussed in Sec. 3.4. Theorem proving allows for abstractions such that verification results obtained at higher levels, thus scalable to large systems, also hold without further proof on refined implementations of these models at lower levels. This is a major strength of theorem proving resulting from the general use of mathematical logic.

Degree of Automation: High manual effort requiring advanced expertise is unfortunately the severe limitation of theorem proving. While golden models of hardware designs are described at the RTL in languages like VHDL or Verilog, theorem provers demand modeling the system and its properties in first order or higher order logic. This is considered disruptive in standard industrial design flows and requires a team of experts.

An industry setting generally requires more automation and support for the standardized description languages than what is offered by general-purpose theorem provers. Theorem provers used in industry today are therefore either tailored to specific niches, such as floating-point units, or they make use of the more automated model checking methods described above. In the latter case, the limitations associated with these more automated techniques apply, as described above.

Coverage: Coverage, in principle, is the great strength of theorem proving. If the entire system is represented by mathematical logic, global verification targets can be fully covered. More than any other method, theorem proving can create connections between different abstraction layers and between hardware and software such that well-defined formal relationships exist between the different levels. This was demonstrated, for example, in the national BMBF projects Verisoft and Verisoft-XT [49]. In the hardware domain, however, the great challenge remains to connect these mathematical models with the concrete descriptions of microarchitectural implementations, in particular the RTL descriptions of the golden models for sign-off. This connection is hard to realize and, if not properly addressed, creates a verification gap because only mathematical models and not the concrete implementations are verified. There is the vision to generate the RTL descriptions for the implementation correct-by-construction from the logic models. However, this faces limited acceptance in the hardware community since design experts wish to leverage their human expertise for design refinements and architectural optimizations. This process relies on standardized hardware description languages such as Verilog and SystemVerilog which are tailored towards this purpose.

### 3.4. The Role of Abstraction in Formal Hardware Verification

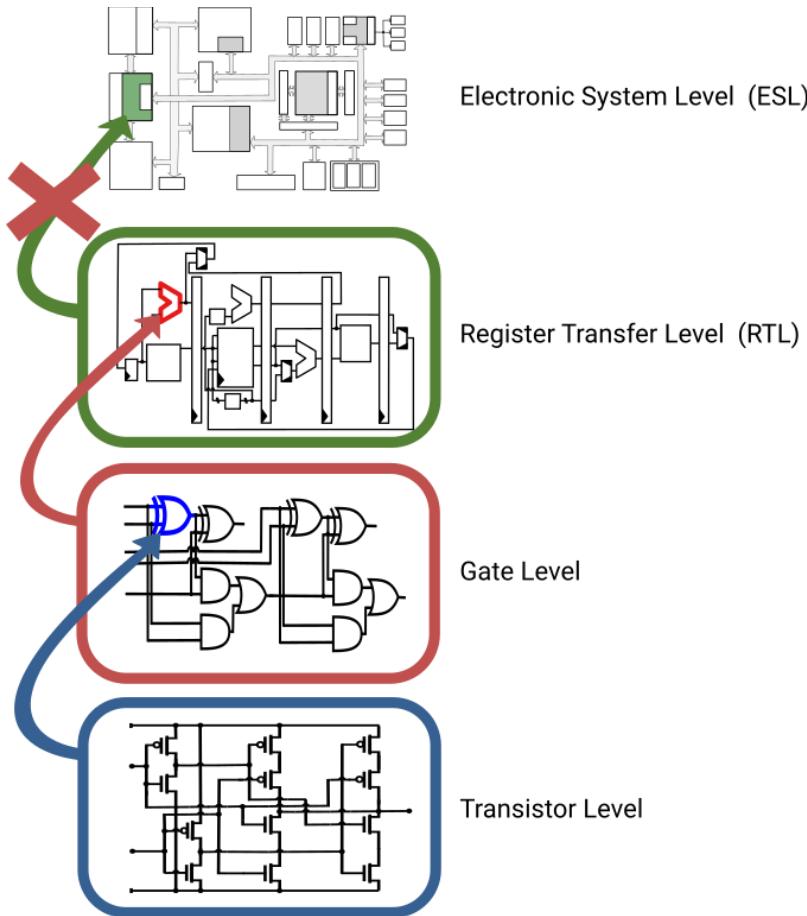

Reasoning in complex digital systems is done through a hierarchy of model descriptions at different levels of abstraction, ranging from transistor-level descriptions through gate-level and RTL to electronic system level (ESL) descriptions. In programmable systems the ISA level serves as the interface between hardware and software. Also the software can be considered at different levels ranging from a hardware-dependent assembler level to hardware-independent descriptions based on high-level programming languages.

Choosing the right level of abstraction for a given verification task is of key importance. Low-level descriptions allow for the verification of local but detailed implementation properties while high-level descriptions facilitate the global analysis of a system's behavior.

Figure 3: Hardware abstraction levels – bottom up reasoning in verification

For hardware the relationships between abstraction layers are summarized in Figure 3. In verification the reasoning is traditionally bottom-up. A new abstraction level can be used for design and verification only when it stands in a well-defined relationship with the lower abstraction levels. Otherwise, the semantics of the abstract model cannot be understood in terms of the „real” circuit to be implemented. Therefore, the verification at each level must build confidence in the model of the next higher level. For example, starting at the transistor level, verification, such as by analog simulation techniques, is used to achieve confidence in the correct behavior of a logic gate, such as a NAND gate. This trust in the NAND gate is not only important at the transistor level. It allows us to move to the next higher level, the gate level and to analyze the behavior of a large gate netlist only in terms of its abstract logic behavior. By merit of trust in the correct transistor-level implementation of the NAND gate, the results of the *logic* simulation extend also to the transistor-level implementation *without further proof*. We say that the gate netlist description is a „sound abstraction” of the transistor-level implementation. Similarly, by merit of formal equivalence checking, the gate netlist is set into a well-defined formal relationship with the RTL models of a design. This makes also RTL a sound abstraction of the physical circuit implementation and justifies the role of RTL descriptions as the golden model in today's design and verification flows.

Unfortunately, the „chain of trust” breaks when considering even higher levels. Descriptions at the electronic system level (ESL) normally lack a well-defined relationship with RTL. While ESL models are of great value for early design exploration and for parallelizing hardware and software development,

ESL abstractions are not formally sound with respect to RTL. Verification results obtained at the ESL level do not necessarily hold for the RTL design models. This „semantic gap“ is one of the main hurdles in today’s flows when attempting to lift design and verification to higher levels than RTL. Even at the presence of high-level synthesis, RTL typically remains the point of reference for sign-off verification. Higher-level models, on the other hand, only serve as early “prototypes” of the system.

As pointed out in Sec. 3.3, theorem proving and mathematical logic, in principle, can provide a complete and sound stack of models for both hardware and software descriptions. In fact, theorem proving also has the potential to close the semantic gap between RTL and ESL models. Industrial adoption of such an approach, however, is difficult since, as explained in Sec. 3.3, theorem proving is not easily compatible with today’s design flows that are based on other languages, modeling techniques and tools.

In order to overcome this limitation, approaches based on path predicate abstraction [60] and instruction-level abstraction [61] have been developed to close the semantic gap between ESL models and RTL exclusively with commonly accepted and standardized design and verification languages. While such approaches successfully connect transaction-level behavioral models with RTL, they do not cover all common abstraction features of high-level models. Therefore, in summary, leveraging the advantages of high-level hardware models for a better scalability of formal verification of concrete design implementations remains one of the main challenges in today’s flows.

### 3.5. Formal Security Verification by Targeting Non-Functional Properties

Most commonly, security verification for hardware has become part of the verification of functional correctness. This means that the characteristics of conventional verification flows for functional correctness, as described in previous sections, apply also to verifying security features.

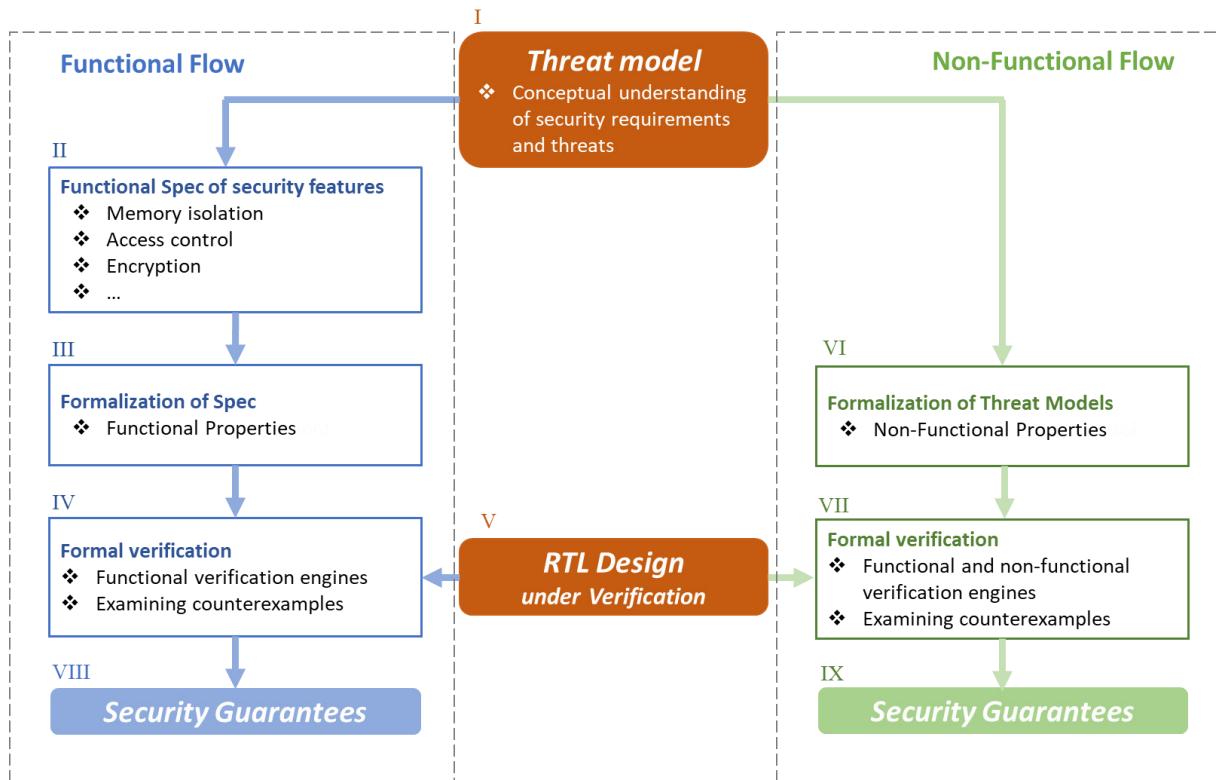

Figure 4: Functional vs. Non-functional verification flow for security

Besides detecting security-critical design bugs (cf. 2.1.1) functional verification techniques can equally detect trojans that are visible at the RTL. Especially techniques using advanced coverage metrics

(cf. 3.2.2.2.2) prove adequate to detect not only any violation of the functional specification but also any additional (undocumented) and possibly malicious functionality that may be triggered only under special circumstances. This holds also for infrastructures used in debugging and test. In special cases, however, tailor-made methods for security analysis, for example for reconfigurable scan networks [62], can be advisable.

In general, if the RTL description is available for analysis, the risk of RTL trojans, as opposed to trojans introduced after sign-off (cf. Lot 4), is usually managed in the same way as the risk of security-critical design bugs. State-of-the-art property checking can be used to verify the design's functionality together with its security features. If the RTL description is not provided, this is a greater challenge. It needs to be addressed in the verification flow by appropriate threat models, as described in Sec. 2.3, taking into account the possibly malicious role of third-party IPs.

The conventional flow for security verification based on functional property checking is shown in the left part of Figure 4. The targeted security features (Box II) typically result from a high-level, architectural perspective. The design specification is extended by an additional *functional* specification (Box III) of these security features which guides their integration into the RTL implementation. This is followed by functional verification procedures (Box IV) which are rooted in established methodologies, as described in Sec. 3.2, for checking an implementation against the functional specification.

It turns out, however, that this classic approach is not always sufficient. Not only does conventional functional verification miss side channels, also the abstract security requirements can be extremely difficult to map to functional specifications, requiring a detailed, microarchitectural understanding of security threats. Therefore, the specification (Box II) itself may miss to cover relevant aspects of the global threat model. Experience shows that, even when choosing security features conservatively, the conventional design process can miss subtle, yet hazardous security gaps and gives rise to the widely spread complaint about a never-ending “patch-and-pray” cycle.

Therefore, another approach to formal hardware security verification has moved into the focus of research which targets security properties directly. This flow is shown on the right side of Figure 4. Instead of developing a detailed (and error-prone) functional specification, this approach starts from the applicable threat model (Box I) and formalizes security requirements rather than detailed functional behaviors (cf. Sec. 2.3). This leads to specifying non-functional security properties (Box VI) which are orthogonal to conventional functional specifications. Since these properties directly target global security requirements without the need of a functional specification for the intended defense mechanisms, these methods have the potential to cover security breaches which are easily missed by the conventional approach. Both conventional solvers for functional verification (cf. Sec. 3.2) as well as specialized solvers, such as [63], can serve as a basis to extend formal hardware verification for such non-functional targets (Box VII).

This relatively new category of formal security verification methods often adopts the view of “information flow tracking” or “taint analysis” which have been popular in the software domain already for a long time. The adoption of taint analysis in the hardware domain was proposed in [64], extending over previous work [65] and the work of [66]. In this paradigm, hazardous information flows are identified between different components of the hardware system and formalized in terms of “information flow properties” or “non-interference properties”. This relates to the notion of “hyperproperties” in SW security verification [67]. Formal hardware verification methods based on the same or similar solvers as in Sec. 3.2 are then used to check these properties.

Commercial EDA companies support this non-functional paradigm by providing tools for *formal path analysis*. These tools check whether or not an illegal information flow can happen through a certain suspicious path between two points in the design. This can be effective in checking selected paths of a

design for information leakages, but faces limitations with so far unknown security weaknesses or unexpected information flows. In order to select a suspicious path, the user must rely on a priori knowledge about potential vulnerabilities. Moreover, experience shows that these methods often suffer from scalability issues when considering global information flows in complex designs, limiting their applicability in practice.

A different approach is taken by a recently proposed method, called Unique Program Execution Checking (UPEC) [68], [69], [70]. UPEC does not decompose the problem in terms of structural paths, but “semantically” in terms of possible propagation scenarios for confidential information. This makes UPEC exhaustive with respect to the formalized threat models and has the advantage that no a priori knowledge on possible attacks is required. Technically, UPEC can be understood as a light-weight form of sequential equivalence checking and therefore partly inherits the high scalability of established methods for equivalence checking. UPEC uses IPC as its underlying proof engine. Therefore, similar as for IPC, also UPEC may cause false alarms which have to be removed by the use of invariants. This inhibits the full automation of the UPEC approach.

Other approaches [71], [72], [73], [74] have targeted verifying hardware security by non-functional properties specified at abstract levels above the RTL. InSpectre [72] provided a framework for formal reasoning about different security countermeasures, using a formal microarchitectural model with speculative and out-of-order execution semantics. Also UCLID [73] can be used to verify the security of different microarchitectural design schemes. CheckMate [74] is a program-synthesis based technique to synthesize attacks based on certain execution patterns and abstract microarchitecture models. The synthesized attacks can be used to test the security of the system. This class of techniques provides important insight into the design flow by an early capturing of security problems and consequently delivering RTL designs with higher quality leading to lower RTL verification efforts. However, these techniques operate on abstractions that lack formal soundness with respect to RTL, as discussed in Sec. 3.4. Therefore, they can miss security-critical details and cannot serve as tools for sign-off verification.

### 3.6. Language-based HW security

Another line of research is language-based security. This paradigm supports hardware design with formal guarantees for security properties and advocates the use of new security-driven hardware description languages. These languages usually use a type system that forbids explicit (direct value assignment) and/or implicit (conditional assignment) information flows between certain security types (security labels), according to a security policy.

Caisson [75] and Sapper [76] are examples of hardware description languages for security. They enable the user to design hardware with the desired information flow properties. In Caisson and Sapper, the designer must annotate each register in the design with security types (labels). The code can be checked with the designed type system for security violations. Caisson uses a static type system forcing the designer to duplicate the logic for those information paths that violate the type system. Sapper improved over Caisson by using dynamic types. This approach can be linked to theorem proving (cf. Sec. 3.3). The VeriCoq-IFT framework [77] automatically converts the design to the Coq formal language [78] and generates a security property theorem based on an information flow policy. Although this removes the need for using a new hardware description language, the designer still needs to annotate the Coq code with security types.

All of the above languages employ a conservative information tracking scheme in their type system, which creates an overestimate about the possible information flows. This bears the risk of overly conservative and possibly inefficient designs.

SecVerilog [79] extends the Verilog language with a security type system. The designer needs to label storage elements with security types which allow for enforcing information flow properties. SecVerilog implements precise information flow tracking by using predicate analysis and constraint solving. This solves the overestimation problem of other languages. Similar to SecVerilog, ChiselFlow [80] is proposed to extend the Chisel language [81] with a security type system. ChiselFlow partially automates the labeling process to mitigate the incurred manual effort. Although the use of Verilog and Chisel as the base language eases the adoption of the method, the labeling process is complicated and security violations are hard to debug in these approaches. Furthermore, the designer may need to adapt the labels in the design in order to verify different security properties. A considerable effort also results from the need of a system-wide labeling of the RTL design. Such changes of design methodologies in established design teams are usually hard to implement.